EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 599

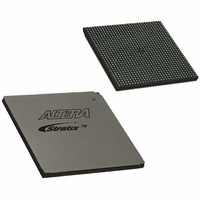

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 599 of 864

- Download datasheet (11Mb)

Altera Corporation

September 2004

Implementing High Performance DSP Functions in Stratix & Stratix GX Devices

required is 16

number of computations per cycle required is 4

there are four polyphase filters, each with four taps.

Figure 7–12. Polyphase Representation of I=4 Interpolation Filter

Polyphase Interpolation Filter Implementation

Figure 7–13

polyphase interpolation filter in

share the same hardware, which is a 4-tap filter. One Stratix or Stratix GX

DSP block can implement one 4-tap filter with 18-bit wide data and

coefficients. A multiplexer can be used to load new coefficient values on

every cycle of the 4 clock. Stratix and Stratix GX phase lock loops (PLLs)

can generate the 4 clock. In the first cycle of the 4 clock, the user needs

to load coefficients for polyphase filter h

Interpolation Using a Single Low-Pass Filter

Interpolation Using a Polyphase Filter

Input

Input

x(n)

x(n)

shows the Stratix or Stratix GX implementation of the

I = 16

I = 4

h(2), h(6), h(10), h(14)

h(3), h(7), h(11), h(15)

h(0), h(4), h(8), h(12)

h(1), h(5), h(9), h(13)

with coefficients

with coefficients

with coefficients

with coefficients

Polyphase filter

Polyphase filter

Polyphase filter

Polyphase filter

4 = 64. In the polyphase implementation, the

Figure

4x Clock

h(0), h(1), ... h(15)

coefficients

y4(n)

y1(n)

y2(n)

y3(n)

Stratix Device Handbook, Volume 2

7–12. The four polyphase filters

0

LPF with

(n); in the second cycle of the 4

initialized at 0

Modulo 4 up

counter

4 = 16. This is because

0

2

3

1

Output

y(n)

Output

y(n)

7–21

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: