EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 770

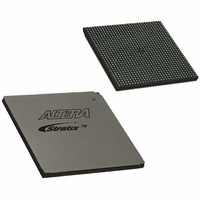

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 770 of 864

- Download datasheet (11Mb)

Device Configuration Pins

11–52

Stratix Device Handbook, Volume 2

nIO_PULLUP

MSEL

nCONFIG

Table 11–15. Dedicated Configuration Pins on the Stratix or Stratix GX Device

Pin Name

[2..0]

N/A

N/A

N/A

User Mode

All

All

All

Configuration

Scheme

Input

Input

Input

Pin Type

Dedicated input that chooses whether the

internal pull-ups on the user I/Os and dual-

purpose I/Os (

RDYnBSY

INIT_DONE

off before and during configuration. A logic high

(1.5-V, 1.8-V, 2.5-V, 3.3-V) turns off the weak

internal pull-ups, while a logic low turns them

on.

The

V

resistor that is always active.

3-bit configuration input that sets the Stratix or

Stratix GX device configuration scheme. See

Table 11–2

These pins can be connected to V

I/O bank they reside in or ground. This pin uses

Schmitt trigger input buffers.

Configuration control input. Pulling this pin low

during user-mode causes the FPGA to lose its

configuration data, enter a reset state, tri-state

all I/O pins. Returning this pin to a logic high

level initiates a reconfiguration.

If your configuration scheme uses an

enhanced configuration device or EPC2

device,

to the configuration device’s

pin. This pin uses Schmitt trigger input buffers.

C C I N T

nIO_PULLUP

nCONFIG

and has an internal 2.5 k pull-down

,

nCS

for the appropriate connections.

,

DEV_OE

DATA[7..0]

,

CS

Description

can be tied directly to V

,

input buffer is powered by

RUnLU

(Part 2 of 8)

,

DEV_CLR

Altera Corporation

,

PGM[]

nINIT_CONF

,

nWS

) are on or

C C I O

,

,

nRS

CLKUSR

July 2005

of the

,

C C

or

,

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: