EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 636

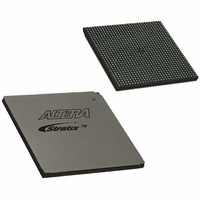

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 636 of 864

- Download datasheet (11Mb)

Discrete Cosine Transform (DCT)

7–58

Stratix Device Handbook, Volume 2

Figure 7–36. Details on the Implementation of the Multiply-Addition Operation

in Stage 4 of the 1-D DCT Algorithm

Note to

(1)

DCT Implementation Results

Table 7–18

precision, as shown in

DCT Design Example

Download the 2-D convolutional filter (d_dct.zip) design example from

the Design Examples section of the Altera web site at www.altera.com.

Part

Utilization

Performance

Latency

Table 7–18. 2-D DCT Implementation Results

Referring to

matrix coefficient. C

Figure

DSP Block - Four-Multipliers Adder Mode (18-bit)

C

S3

C

S3

C

S3

C

S3

shows the results of implementing a 2-D DCT with 18-bit

m4

m2

m3

m1

2

3

4

1

7–36:

Figure

7–33. S3

x

EP1S20F780

Lcell: 1717/18460 (9%)

DSP Block 9-bit element: 18/80 (22%)

Memory bits: 2816/1669248 (<1%)

165 MHz

80 clock cycles

= cos (x /16).

Figure

n

is an output from stage 3 of the DCT and C

7–35.

Altera Corporation

September 2004

y

k

mn

is a

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: