EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 653

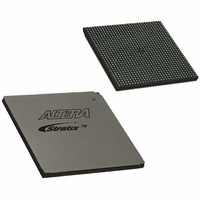

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 653 of 864

- Download datasheet (11Mb)

Figure 8–7. Stratix & Stratix GX Device XSBI Receiver Implementation

Altera Corporation

July 2005

Stratix & Stratix GX PCS Receiver

Stratix & Stratix GX

Logic Array

f

Fast PLL

4 or 8

4 or 8

Stratix and Stratix GX devices contain up to eight fast PLLs. These PLLs

provide high-speed outputs for high-speed differential I/O support as

well as general- purpose clocking with multiplication and phase shifting.

The fast PLL incorporates this 180° phase shift. The Stratix and Stratix GX

device’s data realignment feature enables you to save more logic

elements (LEs). This feature provides a byte-alignment capability, which

is embedded inside the SERDES. The data realignment circuitry can

correct for bit misalignments by slipping data bits.

For more information about fast PLLs, see the Stratix Device Family Data

Sheet section of the Stratix Device Handbook, Volume 1 or the Stratix GX

Device Family Data Sheet section of the Stratix GX Device Handbook,

Volume 1.

Stratix & Stratix GX SERDES

÷J

Register

Parallel

Implementing 10-Gigabit Ethernet Using Stratix & Stratix GX Devices

622 MHz

× W

Parallel-to-Serial

Register

W = 1

CH15

J = 4 or 8

CH0

Stratix Device Handbook, Volume 2

PMA_RXCLK_SRC

RX_D[15]

622 Mbps

622 MHz

RX_D[0]

Receiver

PMA

8–9

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: