EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 572

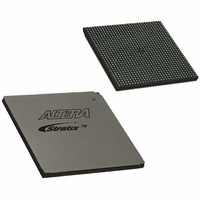

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 572 of 864

- Download datasheet (11Mb)

Operational Modes

Figure 6–12. Multiply Accumulator Mode

Note to

(1)

6–22

Stratix Device Handbook, Volume 2

Data B

Data A

The signa and signb signals are the same in the multiplier stage and the adder/output block.

shiftoutb

Figure

6–12:

shiftinb

shiftouta

ENA

ENA

D

D

CLRN

CLRN

shiftina

Q

Q

signa (1)

signb (1)

Multiply Accumulator Mode

In multiply accumulator mode, the output of the multiplier stage feeds

the adder/output block, which is configured as an accumulator or

subtractor (see

18-bit multiply accumulators in one DSP block. The Quartus II software

implements smaller multiplier-accumulators by tying the unused low-

order bits of an 18-bit multiplier to ground.

The multiply accumulator output can be up to 52 bits wide for a

maximum 36-bit result with 16-bits of accumulation. In this mode, the

DSP block uses output registers and the accum_sload and overflow

signals. The accum_sload[1..0] signal synchronously loads the

multiplier result to the accumulator output. This signal can be

unregistered or registered once or twice. The DSP block can then begin a

new accumulation without losing any clock cycles. The overflow signal

indicates an overflow or underflow in the accumulator. This signal is

clock

aclr

ena

Figure

ENA

D

CLRN

6–12). You can implement up to two independent

Q

accum_sload1

addnsub1

signa

signb

Accumulator

ENA

ENA

D

D

CLRN

CLRN

Altera Corporation

Q

Q

Data Out

overflow

July 2005

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: