EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 367

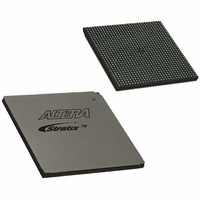

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 367 of 864

- Download datasheet (11Mb)

Revision History

Altera Corporation

Chapter

2

April 2004, v3.0

July 2005, v3.3

July 2003, v2.0

January 2005,

Date/Version

September

2004, v3.1

v3.2

This section provides information on the TriMatrix

blocks internal to Stratix

interfaces.

It contains the following chapters:

■

■

The QDR SRAM Controller Reference Design for Stratix & Stratix GX Devices

chapter is removed in this version of the Stratix Device Handbook. The

information is available in AN 349: Interfacing QDR SRAM with Stratix and

Stratix GX Devices.

The table below shows the revision history for

●

●

●

●

●

●

●

●

●

●

●

Updated

Minor technical content update.

Updated Note 1 in

Updated description about using two different clocks in a

dual-port RAM on

Deleted description of M-RAM block and document

references on

Synchronous occurrences are renamed to pipelined.

Pseudo-synchronous occurrences are renamed flow-

through.

Added AND gate to

Updated performance specification for TriMatrix memory

in Table 2-1.

Added addressing example for a RAM that is using

mixed-width mode, page 2-9.

Added Note 1 to Tables 2-9 and 2-10, Note 3 to Figure 2-

11, and Note 2 to Figures 2-12 and 2-13.

Chapter 2, TriMatrix Embedded Memory Blocks in

Stratix & Stratix GX Devices

Chapter 3, External Memory Interfaces in Stratix & Stratix GX

Devices

“Implementing True Dual-Port Mode”

page

page

Figure 2–12 on page

Changes Made

2–27.

Figure

®

2–27.

devices and the supported external memory

2–12.

Section II. Memory

2–22.

section.

Chapters 2

™

Embedded Memory

and 3.

Comments

Section II–1

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: