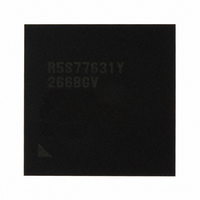

R5S77631Y266BGV Renesas Electronics America, R5S77631Y266BGV Datasheet - Page 26

R5S77631Y266BGV

Manufacturer Part Number

R5S77631Y266BGV

Description

IC SUPERH MPU ROMLESS 499BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R5S77631Y266BGV.pdf

(2056 pages)

Specifications of R5S77631Y266BGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

266MHz

Connectivity

Audio Codec, I²C, MMC, SCI, SIM, SIO, SSI, USB

Peripherals

DMA, LCD, POR, WDT

Number Of I /o

107

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

1.15 V ~ 1.35 V

Data Converters

A/D 4x10b; D/A 2x8b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

499-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R5S77631Y266BGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 26 of 2056

- Download datasheet (10Mb)

25.3 Register Descriptions....................................................................................................... 1002

25.4 Operation ......................................................................................................................... 1017

Section 26 I

26.1 Features............................................................................................................................ 1027

26.2 Input/Output Pins............................................................................................................. 1028

26.3 Register Descriptions....................................................................................................... 1028

26.4 Operations........................................................................................................................ 1046

26.5 Programming Examples................................................................................................... 1056

Rev. 2.00 May 22, 2009 Page xxiv of lxviii

25.3.1 Mode Registers 0, 1 (STIMDR0, STIMDR1)..................................................... 1004

25.3.2 Control Registers 0, 1 (STICR0, STICR1) ......................................................... 1008

25.3.3 Interrupt Status Registers 0, 1 (STIISR0, STIISR1) ........................................... 1009

25.3.4 Interrupt Enable Registers 0, 1 (STIIER0, STIIER1) ......................................... 1011

25.3.5 Time Stamp Counter Registers 0, 1 (STITSC0, STITSC1) ................................ 1013

25.3.6 Transmit/Receive Packet Count Registers 0, 1 (STIPNR0, STIPNR1) .............. 1014

25.3.7 Transmit/Receive Packet Counter Registers 0, 1 (STIPCR0, STIPCR1) ........... 1015

25.3.8 Transmit/Receive FIFO Data Registers 0, 1 (STIFIFO0, STIFIFO1) ................ 1016

25.4.1 External Memory Configuration for Stream Data Transmission/Reception....... 1017

25.4.2 Stream Data Receive Operation.......................................................................... 1018

25.4.3 Stream Data Transmit Operation ........................................................................ 1022

26.3.1 Slave Control Register (ICSCR)......................................................................... 1031

26.3.2 Slave Status Register (ICSSR)............................................................................ 1033

26.3.3 Slave Interrupt Enable Register (ICSIER) .......................................................... 1036

26.3.4 Slave Address Register (ICSAR)........................................................................ 1037

26.3.5 Master Control Register (ICMCR) ..................................................................... 1038

26.3.6 Master Status Register (ICMSR) ........................................................................ 1040

26.3.7 Master Interrupt Enable Register (ICMIER) ...................................................... 1042

26.3.8 Master Address Register (ICMAR) .................................................................... 1043

26.3.9 Clock Control Register (ICCCR)........................................................................ 1043

26.3.10 Receive and Transmit Data Registers (ICRXD and ICTXD) ............................. 1045

26.4.1 Data and Clock Filters ........................................................................................ 1046

26.4.2 Clock Generator.................................................................................................. 1046

26.4.3 Master/Slave Interfaces....................................................................................... 1046

26.4.4 Software Status Interlocking............................................................................... 1046

26.4.5 I

26.4.6 7-Bit Address Format.......................................................................................... 1049

26.4.7 10-Bit Address Format........................................................................................ 1050

26.4.8 Master Transmit Operation................................................................................. 1052

26.4.9 Master Receive Operation .................................................................................. 1054

26.5.1 Master Transmitter.............................................................................................. 1056

2

2

C Bus Data Format ........................................................................................... 1048

C Bus Interface (IIC)................................................................... 1027

Related parts for R5S77631Y266BGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: