AT89C51SND2C-7FTUL Atmel, AT89C51SND2C-7FTUL Datasheet - Page 126

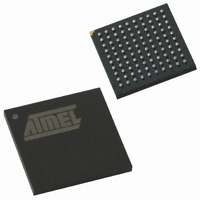

AT89C51SND2C-7FTUL

Manufacturer Part Number

AT89C51SND2C-7FTUL

Description

IC 8051 MCU FLASH 64K MP3 100BGA

Manufacturer

Atmel

Series

89Cr

Datasheet

1.AT89C51SND2C-7FTUL.pdf

(242 pages)

Specifications of AT89C51SND2C-7FTUL

Core Processor

8051

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IDE/ATAPI, MMC, SPI, UART/USART, USB

Peripherals

Audio, I²S, MP3, PCM, POR, WDT

Number Of I /o

32

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.3 V

Data Converters

A/D 2x10b; D/A 2x20b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

ATAPI, I2S, IDE, SPI, UART, USB

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

32

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

AT89C51SND2C7FTUL

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89C51SND2C-7FTUL

Manufacturer:

ATMEL

Quantity:

4 371

126

Bit Number

DIR

7

7

6

5

4

3

2

1

0

AT8xC51SND2C/MP3B

Bit Mnemonic

RXOUTB1

RXOUTB1

RXSETUP

RXOUTB0

STALLRQ

STLCRC

TXCMP

TXRDY

DIR

6

Table 1. UEPSTAX Register

UEPSTAX (S:CEh) – USB Endpoint X Status and Control Register (X = EPNUM set in UEPNUM

Reset Value = 0000 0000b

Description

Control Endpoint Direction Bit

This bit is relevant only if the endpoint is configured in Control type.

Set for the data stage. Clear otherwise.

Note: This bit should be configured on RXSETUP interrupt before any other bit is changed. This also determines

the status phase (IN for a control write and OUT for a control read). This bit should be cleared for status stage of

a Control Out transaction.

Received OUT Data Bank 1 for Endpoints 1 and 2 (Ping-pong mode)

This bit is set by hardware after a new packet has been stored in the endpoint FIFO data bank 1 (only in Ping-

pong mode). Then, the endpoint interrupt is triggered if enabled and all the following OUT packets to the endpoint

bank 1 are rejected (NAK’ed) until this bit has been cleared, excepted for Isochronous Endpoints.

This bit should be cleared by the device firmware after reading the OUT data from the endpoint FIFO.

Stall Handshake Request Bit

Set to send a STALL answer to the host for the next handshake. Clear otherwise.

TX Packet Ready Control Bit

Set after a packet has been written into the endpoint FIFO for IN data transfers. Data should be written into the

endpoint FIFO only after this bit has been cleared. Set this bit without writing data to the endpoint FIFO to send a

Zero Length Packet, which is generally recommended and may be required to terminate a transfer when the

length of the last data packet is equal to MaxPacketSize (e.g. for control read transfers).

Cleared by hardware, as soon as the packet has been sent for Isochronous endpoints, or after the host has

acknowledged the packet for Control, Bulk and Interrupt endpoints.

Stall Sent Interrupt Flag/CRC Error Interrupt Flag

For Control, Bulk and Interrupt Endpoints:

Set by hardware after a STALL handshake has been sent as requested by STALLRQ. Then, the endpoint interrupt

is triggered if enabled in UEPIEN.

Cleared by hardware when a SETUP packet is received (see RXSETUP).

For Isochronous Endpoints:

Set by hardware if the last data received is corrupted (CRC error on data). Then, the endpoint interrupt is

triggered if enabled in UEPIEN.

Cleared by hardware when a non corrupted data is received.

Received SETUP Interrupt Flag

Set by hardware when a valid SETUP packet has been received from the host. Then, all the other bits of the

register are cleared by hardware and the endpoint interrupt is triggered if enabled in UEPIEN.

Clear by software after reading the SETUP data from the endpoint FIFO.

Received OUT Data Bank 0 (see also RXOUTB1 bit for Ping-pong Endpoints)

This bit is set by hardware after a new packet has been stored in the endpoint FIFO data bank 0. Then, the

endpoint interrupt is triggered if enabled and all the following OUT packets to the endpoint bank 0 are rejected

(NAK’ed) until this bit has been cleared, excepted for Isochronous Endpoints. However, for control endpoints, an

early SETUP transaction may overwrite the content of the endpoint FIFO, even if its Data packet is received while

this bit is set.

This bit should be cleared by the device firmware after reading the OUT data from the endpoint FIFO.

Transmitted IN Data Complete Interrupt Flag

Set by hardware after an IN packet has been transmitted for Isochronous endpoints and after it has been

accepted (ACK’ed) by the host for Control, Bulk and Interrupt endpoints. Then, the endpoint interrupt is triggered

if enabled in UEPIEN.

Clear by software before setting again TXRDY.

STALLRQ

5

TXRDY

4

STLCRC

3

RXSETUP

2

RXOUTB0

1

4341H–MP3–10/07

TXCMP

)

0