AT89C51SND2C-7FTUL Atmel, AT89C51SND2C-7FTUL Datasheet - Page 200

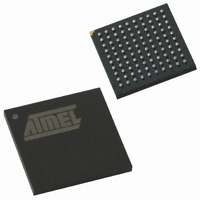

AT89C51SND2C-7FTUL

Manufacturer Part Number

AT89C51SND2C-7FTUL

Description

IC 8051 MCU FLASH 64K MP3 100BGA

Manufacturer

Atmel

Series

89Cr

Datasheet

1.AT89C51SND2C-7FTUL.pdf

(242 pages)

Specifications of AT89C51SND2C-7FTUL

Core Processor

8051

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IDE/ATAPI, MMC, SPI, UART/USART, USB

Peripherals

Audio, I²S, MP3, PCM, POR, WDT

Number Of I /o

32

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.3 V

Data Converters

A/D 2x10b; D/A 2x20b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

ATAPI, I2S, IDE, SPI, UART, USB

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

32

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

AT89C51SND2C7FTUL

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89C51SND2C-7FTUL

Manufacturer:

ATMEL

Quantity:

4 371

- Current page: 200 of 242

- Download datasheet (3Mb)

22.1.1

22.1.2

22.1.3

200

AT8xC51SND2C/MP3B

Clock Generator

Channel Selection

Conversion Precision

Figure 22-2. Timing Diagram

The ADC clock is generated by division of the peripheral clock (see details in section “X2 Fea-

ture”, page 14). The division factor is then given by ADCP4:0 bits in ADCLK register. Figure 22-

3 shows the ADC clock generator and its calculation formula

Figure 22-3. ADC Clock Generator and Symbol Caution:

Note:

The channel on which conversion is performed is selected by the ADCS bit in ADCON register

according to Table 2.

Table 2. ADC Channel Selection

The 10-bit precision conversion is achieved by stopping the CPU core activity during conversion

for limiting the digital noise induced by the core. This mode called the Pseudo-Idle mode

enabled by setting the ADIDL bit in ADCON register

Section "Conversion Launching", page 201), the CPU core is stopped until the end of the con-

1. In all cases, the ADC clock frequency may be higher than the maximum F

2. The ADCD value of 0 is equivalent to an ADCD value of 32.

ADEOC

ADSST

CLOCK

ADEN

reported in the section “Analog to Digital Converter”, page 202.

PER

CLK

ADCS

T

0

1

÷ 2

SETUP

T

ADCD4:0

ADCLK

ADCLK

ADCclk

=

(3)

-------------------------

2 ADCD

PERclk

⋅

. Thus, when conversion is launched (see

T

ADC Clock

CONV

(1)

.

Channel

AIN1

AIN0

ADC Clock Symbol

CLOCK

ADCLK

ADC

4341H–MP3–10/07

parameter

(1),(2)

is

Related parts for AT89C51SND2C-7FTUL

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: