AT89C51SND2C-7FTUL Atmel, AT89C51SND2C-7FTUL Datasheet - Page 142

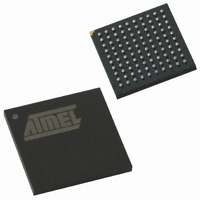

AT89C51SND2C-7FTUL

Manufacturer Part Number

AT89C51SND2C-7FTUL

Description

IC 8051 MCU FLASH 64K MP3 100BGA

Manufacturer

Atmel

Series

89Cr

Datasheet

1.AT89C51SND2C-7FTUL.pdf

(242 pages)

Specifications of AT89C51SND2C-7FTUL

Core Processor

8051

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IDE/ATAPI, MMC, SPI, UART/USART, USB

Peripherals

Audio, I²S, MP3, PCM, POR, WDT

Number Of I /o

32

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.3 V

Data Converters

A/D 2x10b; D/A 2x20b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

ATAPI, I2S, IDE, SPI, UART, USB

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

32

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

AT89C51SND2C7FTUL

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89C51SND2C-7FTUL

Manufacturer:

ATMEL

Quantity:

4 371

- Current page: 142 of 242

- Download datasheet (3Mb)

18.5.2

18.6

142

Data Line Controller

AT8xC51SND2C/MP3B

Command Receiver

Figure 18-13. Command Transmission Flow

The end of the response reception is signalled to you by the EORI flag in MMINT register. This

flag may generate an MMC interrupt request as detailed in Section "Interrupt", page 148. When

this flag is set, 2 other flags in MMSTA register: RESPFS and CRC7S give a status on the

response received. RESPFS indicates if the response format is correct or not: the size is the one

expected (48 bits or 136 bits) and a valid End bit has been received, and CRC7S indicates if the

CRC7 computation is correct or not. These Flags are cleared when a command is sent to the

card and updated when the response has been received.

User may abort response reading by setting and clearing the CRPTR bit in MMCON0 register

which resets the read pointer to the receive FIFO.

According to the MMC specification delay between a command and a response (formally N

parameter) can not exceed 64 MMC clock periods. To avoid any locking of the MMC controller

when card does not send its response (e.g. physically removed from the bus), user must launch

a time-out period to exit from such situation. In case of time-out user may reset the command

controller and its internal state machine by setting and clearing the CCR bit in MMCON2

register.

This time-out may be disarmed when receiving the response.

The data line controller is based on a 16-Byte FIFO used both by the data transmitter channel

and by the data receiver channel.

Configure Response

Transmission

RESPEN = X

CRCDIS = X

Command

RFMT = X

MMCMD = argument

Transmit Command

Load Command in

MMCMD = index

CMDEN = 1

CMDEN = 0

Buffer

4341H–MP3–10/07

CR

Related parts for AT89C51SND2C-7FTUL

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: