AT89C51SND2C-7FTUL Atmel, AT89C51SND2C-7FTUL Datasheet - Page 140

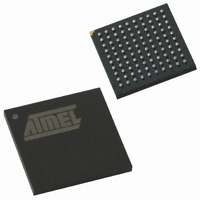

AT89C51SND2C-7FTUL

Manufacturer Part Number

AT89C51SND2C-7FTUL

Description

IC 8051 MCU FLASH 64K MP3 100BGA

Manufacturer

Atmel

Series

89Cr

Datasheet

1.AT89C51SND2C-7FTUL.pdf

(242 pages)

Specifications of AT89C51SND2C-7FTUL

Core Processor

8051

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IDE/ATAPI, MMC, SPI, UART/USART, USB

Peripherals

Audio, I²S, MP3, PCM, POR, WDT

Number Of I /o

32

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.3 V

Data Converters

A/D 2x10b; D/A 2x20b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

ATAPI, I2S, IDE, SPI, UART, USB

Maximum Clock Frequency

40 MHz

Number Of Programmable I/os

32

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

AT89C51SND2C7FTUL

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89C51SND2C-7FTUL

Manufacturer:

ATMEL

Quantity:

4 371

- Current page: 140 of 242

- Download datasheet (3Mb)

Figure 18-9. MMC Controller Block Diagram

18.4

Figure 18-10. MMC Clock Generator and Symbol

Figure 18-11. Configuration Flow

18.5

140

Clock Generator

Command Line Controller

AT8xC51SND2C/MP3B

CLOCK

Internal

OSC

Bus

CLOCK

OSC

MMCON2.7

MMCEN

The MMC clock is generated by division of the oscillator clock (F

troller block as detailed in Section "Oscillator", page 13. The division factor is given by MMCD7:0

bits in MMCLK register, a value of 0x00 stops the MMC clock. Figure 18-10 shows the MMC

clock generator and its output clock calculation formula.

As soon as MMCEN bit in MMCON2 is set, the MMC controller receives its system clock. The

MMC command and data clock is generated on MCLK output and sent to the command line and

data line controllers. Figure 18-11 shows the MMC controller configuration flow.

As exposed in Section “Clock Control”, page 139, MMCD7:0 bits can be used to dynamically

increase or reduce the MMC clock.

As shown in Figure 18-12, the command line controller is divided in 2 channels: the command

transmitter channel that handles the command transmission to the card through the MCMD line

and the command receiver channel that handles the response reception from the card through

the MCMD line. These channels are detailed in the following sections.

Generator

Clock

8

MMCD7:0

MMCLK

Configure MMC Clock

MMC Controller

Configuration

MMCLK = XXh

MMCEN = 1

FLOWC = 0

Command Line

Controller

Controller

Data Line

Controller Clock

MMC Clock

Controller

Interrupt

MMCclk

OSC

MMC Clock Symbol

) issued from the Clock Con-

CLOCK

MMC

=

---------------------------- -

MMCD

MMC

Interrupt

Request

OSCclk

MCLK

MCMD

MDAT

4341H–MP3–10/07

+

1

Related parts for AT89C51SND2C-7FTUL

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: