MC68EC000 Motorola, MC68EC000 Datasheet - Page 23

MC68EC000

Manufacturer Part Number

MC68EC000

Description

Core Processor (SCM 68000)

Manufacturer

Motorola

Datasheet

1.MC68EC000.pdf

(145 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68EC000AA10

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC68EC000AA12

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC68EC000AA16

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC68EC000AA16

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MC68EC000AA16R2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC68EC000AA20

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC68EC000CFU10

Manufacturer:

MOTOROLA/摩托罗拉

Quantity:

20 000

Company:

Part Number:

MC68EC000EI10

Manufacturer:

MOT

Quantity:

6 239

Company:

Part Number:

MC68EC000EI16

Manufacturer:

FREESCALE

Quantity:

450

Company:

Part Number:

MC68EC000EI16

Manufacturer:

Freescale Semiconductor

Quantity:

135

Overview

1.5 DATA ORGANIZATION

The eight data registers support data operands of 1, 8, 16, or 32 bits. The seven address

registers and the active stack pointer support address operands of 32 bits.

1.5.1 Data Registers

Each data register is 32 bits wide. Byte operands occupy the low-order 8 bits, word oper-

ands, the low-order 16 bits, and long-word operands, the entire 32 bits. The least significant

bit is addressed as bit zero; the most significant bit is addressed as bit 31.

When a data register is used as either a source or a destination operand, only the appropri-

ate low-order portion is changed; the remaining high-order portion is neither used nor

changed. For example, if 8 bits are to be moved into a data register, bits 0 through 7 will be

modified and bits 8 through 31 will not be changed.

1.5.2 Address Registers

Each address register (and the stack pointer) is 32 bits wide and holds a full 32-bit address.

Address registers do not support byte-sized operands. Therefore, when an address register

is used as a source operand, either the low-order word or the entire long-word operand is

used, depending upon the operation size. When an address register is used as the destina-

tion operand, the entire register is affected, regardless of the operation size. If the operation

size is word, operands are sign-extended to 32 bits before the operation is performed.

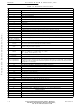

1.5.3 Data Organization In Memory

Bytes are individually addressable. As shown in Figure 1-5, the high-order byte of a word

has the same address as the word. The low-order byte has an odd address, one count

higher. Instructions and multibyte data are accessed only on word (even byte) boundaries.

If a long-word operand is located at address n (n even), then the second word of that oper-

and is located at address n+2.

1-10

ADDRESS

$FFFFFE

$000000

$000002

Figure 1-5. Word Organization in Memory

Freescale Semiconductor, Inc.

EC000 CORE PROCESSOR USER’S MANUAL

For More Information On This Product,

15

14 13 12 11 10 9

Go to: www.freescale.com

BYTE FFFFFE

BYTE 000000

BYTE 000002

WORD 7FFFFF

WORD 0

WORD 1

8

7

6

BYTE FFFFFF

BYTE 000001

BYTE 000003

5

4

3

2 1

0

MOTOROLA