EP1SGX10DF672C5N Altera, EP1SGX10DF672C5N Datasheet - Page 111

EP1SGX10DF672C5N

Manufacturer Part Number

EP1SGX10DF672C5N

Description

IC STRATIX GX FPGA 10KLE 672FBGA

Manufacturer

Altera

Series

Stratix® GXr

Datasheet

1.EP1SGX10CF672C7N.pdf

(272 pages)

Specifications of EP1SGX10DF672C5N

Number Of Logic Elements/cells

10570

Number Of Labs/clbs

1057

Total Ram Bits

920448

Number Of I /o

362

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

672-FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 111 of 272

- Download datasheet (3Mb)

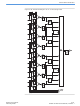

Figure 4–26. Read/Write Clock Mode in Simple Dual-Port Mode

Note to

(1)

Altera Corporation

February 2005

All registers shown except the rden register have asynchronous clear ports.

wraddress[ ]

Figure

address[ ]

byteena[ ]

outclken

wrclock

rdclock

inclken

data[ ]

wren

rden

4–26:

8 LAB Row

Clocks

8

Single-Port Mode

The memory blocks also support single-port mode, used when

simultaneous reads and writes are not required. See

block in a memory block can support up to two single-port mode RAM

blocks in the M4K RAM blocks if each RAM block is less than or equal to

2K bits in size.

D

ENA

D

ENA

D

ENA

D

ENA

D

ENA

D

ENA

Q

Q

Q

Q

Q

Q

Generator

Pulse

Write

Data In

Read Address

Write Address

Byte Enable

Read Enable

Write Enable

Memory Block

Stratix GX Device Handbook, Volume 1

Note (1)

1,024 × 4

2,048 × 2

4,096 × 1

Data Out

256 × 16

512 × 8

D

ENA

Q

Stratix GX Architecture

Figure

To MultiTrack

Interconnect

4–27. A single

4–45

Related parts for EP1SGX10DF672C5N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: