DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 106

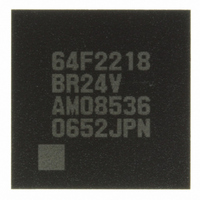

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 106 of 758

- Download datasheet (5Mb)

Notes: 1. Size refers to the operand size.

Table 2.5

Note: * Size refers to the operand size.

Rev.7.00 Dec. 24, 2008 Page 50 of 698

REJ09B0074-0700

Instruction Size*

NEG

EXTU

EXTS

TAS*

Instruction Size*

AND

OR

XOR

NOT

2

B: Byte

W: Word

L: Longword

2. Only register ER0, ER1, ER4, or ER5 should be used when using the TAS instruction.

B: Byte

W: Word

L: Longword

Logic Operations Instructions

B/W/L

W/L

W/L

B

B/W/L

B/W/L

B/W/L

B/W/L

1

Function

0 – Rd → Rd

Takes the two's complement (arithmetic complement) of data in a

general register.

Extends the lower 8 bits of a 16-bit register to word size, or the lower 16

bits of a 32-bit register to longword size, by padding with zeros on the

left.

Extends the lower 8 bits of a 16-bit register to word size, or the lower 16

bits of a 32-bit register to longword size, by extending the sign bit.

@ERd – 0, 1 → (<bit 7> of @ERd)

Tests memory contents, and sets the most significant bit (bit 7) to 1.

Function

Rd ∧ Rs → Rd, Rd ∧ #IMM → Rd

Performs a logical AND operation on a general register and another

general register or immediate data.

Rd ∨ Rs → Rd, Rd ∨ #IMM → Rd

Performs a logical OR operation on a general register and another

general register or immediate data.

Rd ⊕ Rs → Rd, Rd ⊕ #IMM → Rd

Performs a logical exclusive OR operation on a general register and

another general register or immediate data.

∼ Rd → Rd

Takes the one's complement (logical complement) of general register

contents.

Rd (zero extension) → Rd

Rd (sign extension) → Rd

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: