DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 30

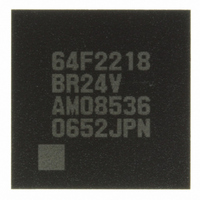

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 30 of 758

- Download datasheet (5Mb)

Section 11 Realtime Clock (RTC)

11.1 Features ............................................................................................................................. 349

11.2 Input/Output Pin ................................................................................................................ 350

11.3 Register Descriptions......................................................................................................... 350

11.4 Operation ........................................................................................................................... 358

11.5 Interrupt Source................................................................................................................. 360

11.6 Operating State in Each Mode........................................................................................... 361

11.7 Usage Notes....................................................................................................................... 362

Section 12 Serial Communication Interface

12.1 Features ............................................................................................................................. 363

12.2 Input/Output Pins .............................................................................................................. 367

12.3 Register Descriptions......................................................................................................... 367

Rev.7.00 Dec. 24, 2008 Page xxviii of liv

REJ09B0074-0700

10.5.1 Notes on Register Access ..................................................................................... 346

10.5.2 Contention between Timer Counter (TCNT) Write and Increment...................... 347

10.5.3 Changing Value of CKS2 to CKS0 ...................................................................... 348

10.5.4 Switching between Watchdog Timer Mode and Interval Timer Mode ................ 348

10.5.5 Internal Reset in Watchdog Timer Mode ............................................................. 348

10.5.6 OVF Flag Clearing in Interval Timer Mode......................................................... 348

11.3.1 Second Data Register (RSECDR) ........................................................................ 350

11.3.2 Minute Data Register (RMINDR) ........................................................................ 351

11.3.3 Hour Data Register (RHRDR).............................................................................. 352

11.3.4 Day-of-Week Data Register (RWKDR)............................................................... 353

11.3.5 RTC Control Register 1 (RTCCR1) ..................................................................... 354

11.3.6 RTC Control Register 2 (RTCCR2) ..................................................................... 355

11.3.7 Clock Source Select Register (RTCCSR) ............................................................ 356

11.3.8 Extended Module Stop Register (EXMDLSTP) .................................................. 357

11.4.1 Initial Settings of Registers after Power-On and Resetting Procedure ................. 358

11.4.2 Time Data Reading Procedure.............................................................................. 359

12.1.1 Block Diagram ..................................................................................................... 365

12.3.1 Receive Shift Register (RSR)............................................................................... 368

12.3.2 Receive Data Register (RDR) .............................................................................. 368

12.3.3 Transmit Data Register (TDR) ............................................................................. 368

12.3.4 Transmit Shift Register (TSR).............................................................................. 368

12.3.5 Serial Mode Register (SMR) ................................................................................ 369

12.3.6 Serial Control Register (SCR) .............................................................................. 373

12.3.7 Serial Status Register (SSR)................................................................................. 377

12.3.8 Smart Card Mode Register (SCMR) .................................................................... 383

12.3.9 Serial Extended Mode Register A_0 (SEMRA_0)............................................... 384

12.3.10 Serial Extended Mode Register B_0 (SEMRB_0) ............................................... 386

.................................................................................. 349

................................................................. 363

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: