DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 26

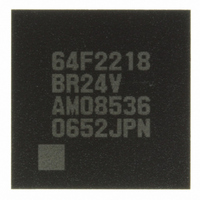

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 26 of 758

- Download datasheet (5Mb)

6.7

6.8

6.9

6.10 Bus Arbitration .................................................................................................................. 155

6.11 Resets and the Bus Controller ........................................................................................... 156

Section 7 DMA Controller (DMAC)

7.1

7.2

7.3

7.4

7.5

7.6

Rev.7.00 Dec. 24, 2008 Page xxiv of liv

REJ09B0074-0700

6.6.2

6.6.3

6.6.4

Burst ROM Interface ......................................................................................................... 147

6.7.1

6.7.2

Idle Cycle .......................................................................................................................... 149

Bus Release ....................................................................................................................... 153

6.9.1

6.10.1 Operation.............................................................................................................. 155

6.10.2 Bus Transfer Timing ............................................................................................ 155

6.10.3 External Bus Release Usage Note ........................................................................ 156

Features ............................................................................................................................. 157

Register Configuration ...................................................................................................... 159

Register Descriptions......................................................................................................... 161

7.3.1

7.3.2

7.3.3

7.3.4

7.3.5

Operation ........................................................................................................................... 177

7.4.1

7.4.2

7.4.3

7.4.4

7.4.5

7.4.6

7.4.7

7.4.8

7.4.9

7.4.10 DMAC Multi-Channel Operation......................................................................... 202

7.4.11 Relation between the DMAC and External Bus Requests.................................... 203

7.4.12 NMI Interrupts and DMAC.................................................................................. 203

7.4.13 Forced Termination of DMAC Operation ............................................................ 204

7.4.14 Clearing Full Address Mode ................................................................................ 205

Interrupts ........................................................................................................................... 206

Usage Notes....................................................................................................................... 207

Valid Strobes ........................................................................................................ 135

Basic Timing ........................................................................................................ 136

Wait Control......................................................................................................... 145

Basic Timing ........................................................................................................ 147

Wait Control......................................................................................................... 149

Bus Release Usage Note....................................................................................... 154

Memory Address Registers (MAR)...................................................................... 161

I/O Address Register (IOAR)............................................................................... 161

Execute Transfer Count Register (ETCR)............................................................ 162

DMA Control Register (DMACR) ....................................................................... 163

DMA Band Control Register (DMABCR)........................................................... 169

Transfer Modes .................................................................................................... 177

Sequential Mode................................................................................................... 178

Idle Mode ............................................................................................................. 181

Repeat Mode ........................................................................................................ 183

Normal Mode ....................................................................................................... 186

Block Transfer Mode............................................................................................ 189

DMAC Activation Sources .................................................................................. 194

Basic DMAC Bus Cycles ..................................................................................... 196

DMAC Bus Cycles (Dual Address Mode) ........................................................... 197

.............................................................................. 157

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: