DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 25

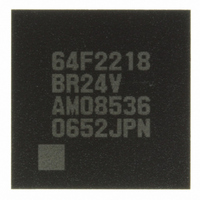

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 25 of 758

- Download datasheet (5Mb)

5.4

5.5

5.6

5.7

Section 6 Bus Controller

6.1

6.2

6.3

6.4

6.5

6.6

5.3.3

5.3.4

Interrupt Sources ............................................................................................................... 99

5.4.1

5.4.2

Interrupt Exception Handling Vector Table...................................................................... 101

Interrupt Control Modes and Interrupt Operation ............................................................. 103

5.6.1

5.6.2

5.6.3

5.6.4

5.6.5

Usage Notes ...................................................................................................................... 112

5.7.1

5.7.2

5.7.3

5.7.4

5.7.5

5.7.6

Features ............................................................................................................................. 115

Input/Output Pins .............................................................................................................. 117

Register Descriptions ........................................................................................................ 118

6.3.1

6.3.2

6.3.3

6.3.4

6.3.5

6.3.6

Bus Control ....................................................................................................................... 127

6.4.1

6.4.2

6.4.3

6.4.4

Basic Timing ..................................................................................................................... 131

6.5.1

6.5.2

6.5.3

Basic Bus Interface ........................................................................................................... 134

6.6.1

IRQ Sense Control Registers H and L (ISCRH, ISCRL)..................................... 96

IRQ Status Register (ISR).................................................................................... 98

External Interrupts ............................................................................................... 99

Internal Interrupts................................................................................................. 100

Interrupt Control Mode 0 ..................................................................................... 103

Interrupt Control Mode 2 ..................................................................................... 105

Interrupt Exception Handling Sequence .............................................................. 107

Interrupt Response Times .................................................................................... 108

DMAC Activation by Interrupt............................................................................ 109

Contention between Interrupt Generation and Disabling..................................... 112

Instructions that Disable Interrupts ...................................................................... 113

Times when Interrupts Are Disabled ................................................................... 113

Interrupts during Execution of EEPMOV Instruction.......................................... 113

IRQ Interrupt........................................................................................................ 113

NMI Interrupt Usage Notes.................................................................................. 114

Bus Width Control Register (ABWCR)............................................................... 118

Access State Control Register (ASTCR) ............................................................. 119

Wait Control Registers H and L (WCRH, WCRL).............................................. 120

Bus Control Register H (BCRH).......................................................................... 124

Bus Control Register L (BCRL) .......................................................................... 125

Pin Function Control Register (PFCR) ................................................................ 126

Area Divisions ..................................................................................................... 127

Bus Specifications................................................................................................ 128

Bus Interface for Each Area................................................................................. 129

Chip Select Signals .............................................................................................. 130

On-Chip Memory (ROM, RAM) Access Timing ................................................ 131

On-Chip Peripheral Module Access Timing........................................................ 132

External Address Space Access Timing............................................................... 133

Data Size and Data Alignment (Supported Only by the H8S/2218 Group)......... 134

.................................................................................................... 115

Rev.7.00 Dec. 24, 2008 Page xxiii of liv

REJ09B0074-0700

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: