DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 534

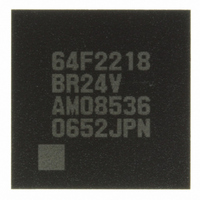

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 534 of 758

- Download datasheet (5Mb)

14.3.10 USB Endpoint Data Register 0o (UEDR0o)

UEDR0o is a data register for endpoint 0 (for Control_out transfer). UEDR0o stores data received

from the host. The number of data items to be read must be the number of bytes specified by

UESZ0o.

When 1 byte is read from UEDR0o, UESZ0o is decremented by1.

UEDR0o is a byte register to which 4-byte address area is assigned. Accordingly, UEDR0o allows

the user to read 2-byte or 4-byte data continuously by word transfer or longword transfer.

14.3.11 USB Endpoint Data Register 3 (UEDR3)

UEDR3 is a data register for endpoint 3 (for Interrupt_in transfer). UEDR3 stores data to be sent to

the host. The number of data items to be written continuously must be the maximum packet size or

less.

UEDR3 is a byte register to which 4-byte address area is assigned. Accordingly, UEDR3 allows

the user to write 2-byte or 4-byte data continuously by word transfer or longword transfer. For

details, see section 2.9.4, Accessing Registers Containing Write-Only Bits.

14.3.12 USB Endpoint Data Register 1 (UEDR1)

UEDR1 is a data register for endpoint 1 (for Bulk_in transfer). UEDR1 stores data to be sent to the

host. The number of data items to be written continuously must be the maximum packet size or

less.

UEDR1 is a byte register to which 4-byte address area is assigned. Accordingly, UEDR1 allows

the user to write 2-byte or 4-byte data continuously by word transfer or longword transfer. For

details, see section 2.9.4, Accessing Registers Containing Write-Only Bits.

Rev.7.00 Dec. 24, 2008 Page 478 of 698

REJ09B0074-0700

Bit

7 to 0 D7 to D0

Bit

7 to 0 D7 to D0

Bit

7 to 0 D7 to D0

Bit Name

Bit Name

Bit Name

Initial Value R/W

—

Initial Value R/W

All 0

Initial Value R/W

All 0

R

W

W

Description

These bits store data for Control_out transfer

Description

These bits store data for Interrupt_in transfer

Description

These bits store data for Bulk_in transfer

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: