DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 751

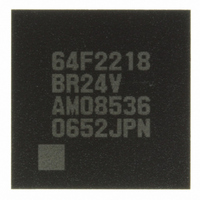

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 751 of 758

- Download datasheet (5Mb)

16-Bit Timer Pulse Unit......................... 273

A/D Conversion Time............................ 544

A/D Converter ....................................... 535

A/D Converter Activation...................... 323

Absolute Address..................................... 59

Address Space.......................................... 38

Addressing Mode..................................... 58

ADI ........................................................ 546

Advanced Mode....................................... 36

Arithmetic Operations Instructions.......... 49

Asynchronous Mode .............................. 403

Bcc ..................................................... 46, 54

Bit Manipulation Instructions .................. 52

Bit rate ................................................... 395

Block Data Transfer Instruction............... 56

Boot Mode ............................................. 567

Boundary Scan....................................... 449

Branch Instructions .................................. 54

Break...................................................... 441

Buffer Operation.................................... 309

Bulk-In Transfer .................................... 513

Bulk-Out Transfer.................................. 515

Bus Arbitration ...................................... 155

Bus cycle................................................ 133

Clock Pulse Generator ........................... 595

Condition Field ........................................ 57

Condition-Code Register ......................... 42

Control Transfer..................................... 506

CPU Operating Modes............................. 34

Data reading procedure.......................... 359

Data Transfer Instructions ....................... 48

DMA Transfer Specifications ................ 520

Effective Address............................... 58, 62

Index

Effective Address Extension.................... 57

Emulation............................................... 577

Erase/Erase-Verify................................. 581

Erasing units .................................. 558, 559

Error Protection...................................... 583

Exception Handling ................................. 81

Extended Control Register (EXR) ........... 41

External Trigger..................................... 545

Flash Memory........................................ 553

Framing error ......................................... 410

Free-running count operation................. 302

General Registers..................................... 40

Hardware Protection .............................. 583

Immediate ................................................ 60

Input Capture Function .......................... 305

Instruction Set.......................................... 45

Internal bus masters ............................... 115

Interrupt Control Mode .......................... 103

Interrupt Controller .................................. 91

Interrupt Exception Handling Vector Table

Interrupt Mask Bit.................................... 42

Interrupt mask level ................................. 41

Interrupt priority register.......................... 91

Interrupt-In Transfer .............................. 512

Interrupts.................................................. 87

Interval Timer Mode.............................. 344

Logic Operations Instructions.................. 50

Mark State.............................................. 442

Masked ROM......................................... 593

Memory cycle ........................................ 131

Memory Indirect ...................................... 61

............................................................ 101

Rev.7.00 Dec. 24, 2008 Page 695 of 698

REJ09B0074-0700

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: