DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 40

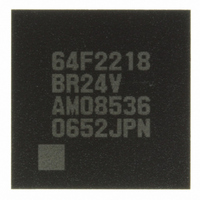

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 40 of 758

- Download datasheet (5Mb)

Section 3 MCU Operating Modes

Figure 3.1

Figure 3.2

Figure 3.3

Figure 3.4

Section 4 Exception Handling

Figure 4.1

Figure 4.2

Figure 4.3

Figure 4.4

Section 5 Interrupt Controller

Figure 5.1

Figure 5.2

Figure 5.3

Figure 5.4

Figure 5.5

Figure 5.6

Figure 5.7

Figure 5.8

Section 6 Bus Controller

Figure 6.1

Figure 6.2

Figure 6.3

Figure 6.4

Figure 6.5

Figure 6.6

Figure 6.7

Figure 6.8

Figure 6.9

Figure 6.10 Bus Timing for 8-Bit 2-State Access Space............................................................ 136

Figure 6.11 Bus Timing for 8-Bit 3-State Access Space (Except Area 6) ................................. 137

Figure 6.12 Bus Timing for Area 6 and RTC............................................................................. 138

Figure 6.13 Bus Timing for 16-Bit 2-State Access Space (1) (Even Address Byte Access) ..... 139

Rev.7.00 Dec. 24, 2008 Page xxxviii of liv

REJ09B0074-0700

Memory Map in Each Operating Mode for HD64F2218, HD64F2218U and

HD64F2218CU....................................................................................................... 77

Memory Map in Each Operating Mode for HD64F2217CU .................................. 78

Memory Map in Each Operating Mode for HD6432217........................................ 79

Memory Map in Each Operating Mode for HD64F2212, HD64F2212U,

HD64F2212CU, HD64F2211, HD64F2211U, HD64F2211CU, HD64F2210CU,

HD6432211, HD6432210 and HD6432210S ......................................................... 80

Reset Sequence (Mode 4) ....................................................................................... 85

Reset Sequence (Modes 6 and 7) ............................................................................ 86

Stack Status after Exception Handling ................................................................... 89

Operation when SP Value Is Odd ........................................................................... 90

Block Diagram of Interrupt Controller ................................................................... 92

Block Diagram of Interrupts IRQn ......................................................................... 99

Timing of Setting IRQnF........................................................................................ 100

Flowchart of Procedure Up to Interrupt Acceptance in Interrupt Control

Mode 0.................................................................................................................... 104

Flowchart of Procedure Up to Interrupt Acceptance in Interrupt Control

Mode 2.................................................................................................................... 106

Interrupt Exception Handling ................................................................................. 107

Interrupt Control for DMAC................................................................................... 110

Contention between Interrupt Generation and Disabling........................................ 112

Block Diagram of Bus Controller ........................................................................... 116

Overview of Area Divisions ................................................................................... 127

CSn Signal Output Timing (n = 0 to 5)................................................................... 130

On-Chip Memory Access Cycle ............................................................................. 131

Pin States during On-Chip Memory Access ........................................................... 132

On-Chip Peripheral Module Access Cycle ............................................................. 132

Pin States during On-Chip Peripheral Module Access ........................................... 133

Access Sizes and Data Alignment Control (8-Bit Access Space)........................... 134

Access Sizes and Data Alignment Control (16-Bit Access Space)......................... 135

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: