DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 466

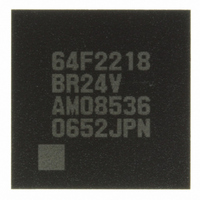

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 466 of 758

- Download datasheet (5Mb)

12.4.6

Figure 12.11 shows an example of operation for reception in asynchronous mode. In serial

reception, the SCI operates as described below.

1. The SCI monitors the communication line. If a start bit is detected, the SCI performs internal

2. If an overrun error occurs (when reception of the next data is completed while the RDRF flag

3. If a parity error is detected, the PER bit in SSR is set to 1 and receive data is transferred to

4. If a framing error is detected (when the stop bit is 0), the FER bit in SSR is set to 1 and receive

5. If reception is completed successfully, the RDRF bit in SSR is set to 1, and receive data is

Table 12.11 shows the states of the SSR status flags and receive data handling when a receive error

is detected. If a receive error is detected, the RDRF flag retains its state before receiving data.

Reception cannot be resumed while a receive error flag is set to 1. Accordingly, clear the ORER,

FER, PER, and RDRF bits to 0 before resuming reception. Figure 12.12 shows a sample flow chart

for serial data reception.

Rev.7.00 Dec. 24, 2008 Page 410 of 698

REJ09B0074-0700

synchronization, receives receive data in RSR, and checks the parity bit and stop bit.

is still set to 1), the ORER bit in SSR is set to 1. If the RIE bit in SCR is set to 1 at this time, an

ERI interrupt request is generated. Receive data is not transferred to RDR. The RDRF flag

remains to be set to 1.

RDR. If the RIE bit in SCR is set to 1 at this time, an ERI interrupt request is generated.

data is transferred to RDR. If the RIE bit in SCR is set to 1 at this time, an ERI interrupt

request is generated.

transferred to RDR. If the RIE bit in SCR is set to 1 at this time, an RXI interrupt request is

generated. Continuous reception is possible because the RXI interrupt routine reads the receive

data transferred to RDR before reception of the next receive data has been completed.

RDRF

FER

Serial Data Reception (Asynchronous Mode)

1

Start

bit

0

D0

Figure 12.11 Example of SCI Operation in Reception

(Example with 8-Bit Data, Parity, One Stop Bit)

D1

1 frame

Data

D7

RXI interrupt

request

generated

Parity

bit

0/1

Stop

bit

1

Start

bit

0

RDR data read and RDRF

flag cleared to 0 in RXI

interrupt service routine

D0

D1

Data

D7

Parity

bit

0/1

ERI interrupt request

generated by framing

error

Stop

bit

0

Idle state

(mark state)

1

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: