DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 379

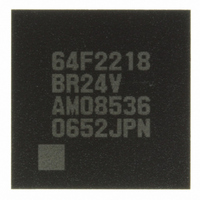

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 379 of 758

- Download datasheet (5Mb)

Input Capture/Compare Match Interrupt: An interrupt is requested if the TGIE bit in TIER is

set to 1 when the TGF flag in TSR is set to 1 by the occurrence of a TGR input capture/compare

match on a particular channel. The interrupt request is cleared by clearing the TGF flag to 0. The

TPU has 8 input capture/compare match interrupts, four each for channel 0, and two each for

channels 1 and 2.

Overflow Interrupt: An interrupt is requested if the TCIEV bit in TIER is set to 1 when the

TCFV flag in TSR is set to 1 by the occurrence of TCNT overflow on a channel. The interrupt

request is cleared by clearing the TCFV flag to 0. The TPU has three overflow interrupts, one for

each channel.

Underflow Interrupt: An interrupt is requested if the TCIEU bit in TIER is set to 1 when the

TCFU flag in TSR is set to 1 by the occurrence of TCNT underflow on a channel. The interrupt

request is cleared by clearing the TCFU flag to 0. The TPU has two underflow interrupts, one each

for channels 1 and 2.

9.6.2

The DMAC can be activated by the TGRA input capture/compare match interrupt for a channel.

For details, see section 7, DMA Controller (DMAC). With the TPU, a total of three TGRA input

capture/compare match interrupts can be used as DMAC activation sources, one for each channel.

9.6.3

The A/D converter can be activated by the TGRA input capture/compare match for a channel. If

the TTGE bit in TIER is set to 1 when the TGFA flag in TSR is set to 1 by the occurrence of a

TGRA input capture/compare match on a particular channel, a request to start A/D conversion is

sent to the A/D converter. If the TPU conversion start trigger has been selected on the A/D

converter side at this time, A/D conversion is started. In the TPU, a total of three TGRA input

capture/compare match interrupts can be used as A/D converter conversion start sources, one for

each channel.

DMAC Activation

A/D Converter Activation

Rev.7.00 Dec. 24, 2008 Page 323 of 698

REJ09B0074-0700

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: