DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 207

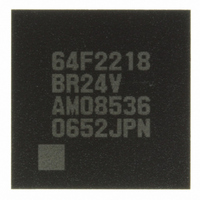

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 207 of 758

- Download datasheet (5Mb)

Write after Read: If an external write occurs after an external read while the ICIS0 bit in BCRH

is set to 1, an idle cycle is inserted at the start of the write cycle.

Figure 6.23 shows an example of the operation in this case. In this example, bus cycle A is a read

cycle from ROM with a long output floating time, and bus cycle B is a CPU write cycle. In (a), an

idle cycle is not inserted, and a collision occurs in cycle B between the read data from ROM and

the CPU write data. In (b), an idle cycle is inserted, and a data collision is prevented.

Relationship between Chip Select (CS) Signal and Read (RD) Signal: Depending on the

system's load conditions, the RD signal may lag behind the CS signal. An example is shown in

figure 6.24.

In this case, with the setting for no idle cycle insertion (a), there may be a period of overlap

between the bus cycle A RD signal and the bus cycle B CS signal.

Setting idle cycle insertion, as in (b), however, will prevent any overlap between the RD and CS

signals.

In the initial state after reset release, idle cycle insertion (b) is set.

Address bus

CS (area A)

CS (area B)

Data bus

HWR

RD

φ

(a) Idle cycle not inserted

(ICIS0 = 0)

T

Bus cycle A

1

Figure 6.23 Example of Idle Cycle Operation (2)

Long output floating time

T

2

T

3

Bus cycle B

T

1

T

2

Data collision

Address bus

CS (area A)

CS (area B)

Data bus

HWR

RD

φ

Rev.7.00 Dec. 24, 2008 Page 151 of 698

T

1

Bus cycle A

(b) Idle cycle inserted

(Initial value ICIS0 = 1)

T

2

T

3

T

Bus cycle B

I

REJ09B0074-0700

T

1

T

2

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: