DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 17

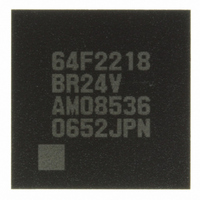

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 17 of 758

- Download datasheet (5Mb)

Item

13.3.2 IDCODE

Register (IDCODE)

Table 13.3 IDCODE

Register Configuration

14.3.5 USB FIFO

Clear Register 0

(UFCLR0)

14.8.16 Clearing the

FIFO when DMA

Transfer Is Enabled

Section 16 RAM

Page

454

475 to

476

533

551

Revision (See Manual for Details)

Description amended

...The HD64F2218, HD64F2218U, HD64F2218CU and

HD64F2217CU output fixed codes H'002A200F from the TDO.

...

Table amended

Bit Table amended

Note added

Note:* When DMA writes are enabled (EP2T1 set to 1 and

Description added

When DMA transfer is enabled (EP2T1 = 1 and EP2T0 = 0 or 1

in UDMAR) at endpoint 2, it is not possible to clear OUTFIFO in

EP2. It is necessary to disable DMA transfer (EP2T1 = 0 and

EP2T0 = 0 in UDMAR) before clearing the FIFO.

Description amended

The HD64F2218, HD64F2218U, and HD64F2218CU have 12

kbytes of on-chip high-speed static RAM. The HD6432217,

HD64F2211, HD64F2211U, and HD64F2211CU have 8 kbytes

of on-chip high-speed static RAM. The HD6432210 and

HD6432210S have 4 kbytes of on-chip high-speed static RAM.

The RAM is connected to the CPU by a 16-bit data bus,

enabling one-state access by the CPU to both byte data and

word data.

EP2T0 set to 0 or 1 in UDMAR), it is not possible to

clear the data in the FIFO by writing 1 to EP2CLR. To

clear the data in the FIFO, disable DMA transfers (clear

EP2T1 and EP2T0 in UDMAR to 0) and then write 1 to

EP2CLR.

Bit

7, 6

5

Bit Name

—

EP2CLR

Initial Value R/W

All 0

0

Bits

HD64F2218,

HD64F2218U,

HD64F2218CU and

HD64F2217CU codes

Contents

Rev.7.00 Dec. 24, 2008 Page xv of liv

R

W

Description

Reserved

These bits are always rea

modified.

EP2 Clear*

0: Performs no operation.

1: Clears EP2 OUT FIFO.

REJ09B0074-0700

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: