DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 682

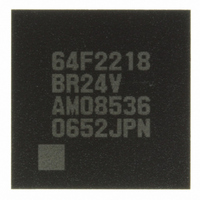

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 682 of 758

- Download datasheet (5Mb)

20.9

20.9.1

When the SLEEP instruction is executed in high-speed mode with the SBYCR SSBY bit = 1,

LPWRCR DTON bit = 1, LSON bit = 1, and TCSR_1 PSS bit = 1, CPU operation shifts to

subactive mode. When an interrupt occurs in watch mode, and if the LSON bit of LPWRCR is 1, a

transition is made to subactive mode. And if an interrupt occurs in subsleep mode, a transition is

made to subactive mode.

In subactive mode, the CPU operates at low speed on the subclock, and the program is executed

step by step. Peripheral modules other than WDT and RTC are also stopped.

When operating the CPU in subactive mode, the SCKCR SCK2 to SCK0 bits must be set to 0.

20.9.2

Subactive mode is exited by the SLEEP instruction or the RES, MRES*, or STBY pin.

• Exiting Subactive Mode by SLEEP Instruction

• Exiting Subactive Mode by RES or MRES* pin

• Exiting Subactive Mode by STBY Pin

Note: * Supported only by the H8S/2218 Group.

Rev.7.00 Dec. 24, 2008 Page 626 of 698

REJ09B0074-0700

When the SLEEP instruction is executed with the SBYCR SSBY bit = 1, LPWRCR DTON bit

= 0, and TCSR_1 PSS bit = 1, the CPU exits subactive mode and a transition is made to watch

mode. When the SLEEP instruction is executed with the SBYCR SSBY bit = 0, LPWRCR

LSON bit = 1, and TCSR_1 PSS bit = 1, a transition is made to subsleep mode. Finally, when

the SLEEP instruction is executed with the SBYCR SSBY bit = 1, LPWRCR DTON bit = 1,

LSON bit = 0, and TCSR_1 PSS bit = 1, a direct transition is made to high-speed mode (SCK0

to SCK2 all 0).

For exiting subactive mode by the RES or MRES* pin, see section 20.4.2, Clearing Software

Standby Mode.

When the STBY pin level is driven low, a transition is made to hardware standby mode.

Subactive Mode

Transition to Subactive Mode

Exiting Subactive Mode

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: