DF2505BR26DV Renesas Electronics America, DF2505BR26DV Datasheet - Page 101

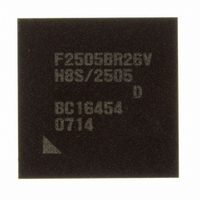

DF2505BR26DV

Manufacturer Part Number

DF2505BR26DV

Description

IC H8S/2505 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2505BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

384KB (384K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2505BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 101 of 980

- Download datasheet (6Mb)

Table 2.11 Addressing Modes

2.7.1

The register field of the instruction specifies an 8-, 16-, or 32-bit general register containing the

operand. R0H to R7H and R0L to R7L can be specified as 8-bit registers. R0 to R7 and E0 to E7

can be specified as 16-bit registers. ER0 to ER7 can be specified as 32-bit registers.

2.7.2

The register field of the instruction code specifies an address register (ERn) which contains the

address of the operand on memory. If the address is a program instruction address, the lower 24

bits are valid and the upper 8 bits are all assumed to be 0 (H'00).

2.7.3

A 16-bit or 32-bit displacement contained in the instruction is added to an address register (ERn)

specified by the register field of the instruction, and the sum gives the address of a memory

operand. A 16-bit displacement is sign-extended when added.

2.7.4

Register indirect with post-increment⎯@ERn+: The register field of the instruction code

specifies an address register (ERn) which contains the address of a memory operand. After the

operand is accessed, 1, 2, or 4 is added to the address register contents and the sum is stored in the

address register. The value added is 1 for byte access, 2 for word transfer instruction, or 4 for

No.

1

2

3

4

5

6

7

8

Register Direct⎯Rn

Register Indirect⎯@ERn

Register Indirect with Displacement⎯@(d:16, ERn) or @(d:32, ERn)

Register Indirect with Post-Increment or Pre-Decrement⎯@ERn+ or @-ERn

Addressing Mode

Register direct

Register indirect

Register indirect with displacement

Register indirect with post-increment

Register indirect with pre-decrement

Absolute address

Immediate

Program-counter relative

Memory indirect

Symbol

Rn

@ERn

@(d:16,ERn)/@(d:32,ERn)

@ERn+

@–ERn

@aa:8/@aa:16/@aa:24/@aa:32

#xx:8/#xx:16/#xx:32

@(d:8,PC)/@(d:16,PC)

@@aa:8

Rev. 6.00 Sep. 24, 2009 Page 53 of 928

REJ09B0099-0600

Section 2 CPU

Related parts for DF2505BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: