DF2505BR26DV Renesas Electronics America, DF2505BR26DV Datasheet - Page 32

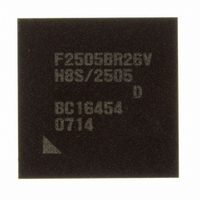

DF2505BR26DV

Manufacturer Part Number

DF2505BR26DV

Description

IC H8S/2505 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2505BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

384KB (384K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2505BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 32 of 980

- Download datasheet (6Mb)

Section 5 Interrupt Controller

Figure 5.1

Figure 5.2

Figure 5.3

Figure 5.4

Figure 5.5

Figure 5.6

Figure 5.7

Figure 5.8

Figure 5.9

Section 6 PC Break Controller (PBC)

Figure 6.1

Figure 6.2

Section 7 Bus Controller

Figure 7.1

Figure 7.2

Figure 7.3

Figure 7.4

Figure 7.5

Figure 7.6

Figure 7.7

Figure 7.8

Figure 7.9

Figure 7.10 On-Chip IEB Module Access Cycle ....................................................................... 142

Figure 7.11 Pin States during On-Chip IEB Module Access...................................................... 143

Figure 7.12 On-Chip HCAN Module Access Cycle................................................................... 143

Figure 7.13 Pin States during On-Chip HCAN Module Access................................................. 144

Figure 7.14 Access Sizes and Data Alignment Control (8-Bit Access Space) ........................... 145

Figure 7.15 Access Sizes and Data Alignment Control (16-Bit Access Space) ......................... 146

Figure 7.16 Bus Timing for 8-Bit 2-State Access Space ............................................................ 147

Figure 7.17 Bus Timing for 8-Bit 3-State Access Space ............................................................ 148

Figure 7.18 Bus Timing for 16-Bit 2-State Access Space (1) (Even Address Byte Access)...... 149

Figure 7.19 Bus Timing for 16-Bit 2-State Access Space (2) (Odd Address Byte Access) ....... 150

Figure 7.20 Bus Timing for 16-Bit 2-State Access Space (3) (Word Access) ........................... 151

Figure 7.21 Bus Timing for 16-Bit 3-State Access Space (1) (Even Address Byte Access)...... 152

Figure 7.22 Bus Timing for 16-Bit 3-State Access Space (2) (Odd Address Byte Access) ....... 153

Figure 7.23 Bus Timing for 16-Bit 3-State Access Space (3) (Word Access) ........................... 154

Figure 7.24 Example of Wait State Insertion Timing................................................................. 156

Rev. 6.00 Sep. 24, 2009 Page xxx of xlvi

REJ09B0099-0600

Block Diagram of Interrupt Controller...................................................................... 86

Block Diagram of IRQ7 to IRQ0 Interrupts.............................................................. 94

Set Timing for IRQ7F to IRQ0F ............................................................................... 95

Block Diagram of Interrupt Control Operation ....................................................... 101

Flowchart of Procedure up to Interrupt Acceptance in Interrupt Control Mode 0 . 104

Flowchart of Procedure up to Interrupt Acceptance in Interrupt Control Mode 2 . 106

Interrupt Exception Handling.................................................................................. 108

DTC and Interrupt Controller.................................................................................. 111

Contention between Interrupt Generation and Disabling ........................................ 113

Block Diagram of PC Break Controller .................................................................. 116

Operation in Power-Down Mode Transitions ......................................................... 120

Block Diagram of Bus Controller ........................................................................... 124

Overview of Area Divisions.................................................................................... 135

CSn Signal Output Timing (n = 0 to 7) ................................................................... 138

On-Chip Memory Access Cycle ............................................................................. 139

Pin States during On-Chip Memory Access............................................................ 140

On-Chip Peripheral Module Access Cycle ............................................................. 140

Pin States during On-Chip Peripheral Module Access............................................ 141

On-Chip Port H, Port J, and IIC2 Module Access Cycle ........................................ 141

Pin States during On-Chip Port H, Port J, and IIC2 Module Access ...................... 142

Related parts for DF2505BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: