DF2505BR26DV Renesas Electronics America, DF2505BR26DV Datasheet - Page 35

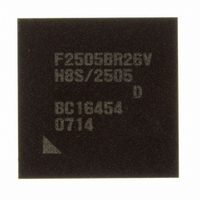

DF2505BR26DV

Manufacturer Part Number

DF2505BR26DV

Description

IC H8S/2505 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2505BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

384KB (384K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2505BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 35 of 980

- Download datasheet (6Mb)

Section 11 8-Bit Timers (TMR)

Figure 11.1 Block Diagram of 8-Bit Timer Module................................................................... 354

Figure 11.2 Example of Pulse Output......................................................................................... 364

Figure 11.3 Count Timing for Internal Clock Input ................................................................... 365

Figure 11.4 Count Timing for External Clock Input .................................................................. 365

Figure 11.5 Timing of CMF Flag Setting ................................................................................... 366

Figure 11.6 Timing of Timer Output.......................................................................................... 366

Figure 11.7 Timing of Compare-Match Clear ............................................................................ 367

Figure 11.8 Timing of Clearing by External Reset Input ........................................................... 367

Figure 11.9 Timing of OVF Setting ........................................................................................... 368

Figure 11.10 Contention between TCNT Write and Clear ........................................................... 371

Figure 11.11 Contention between TCNT Write and Increment.................................................... 372

Figure 11.12 Contention between TCOR Write and Compare-Match ......................................... 373

Section 12 Watchdog Timer (WDT)

Figure 12.1 Block Diagram of WDT_0 (1) ................................................................................ 378

Figure 12.1 Block Diagram of WDT_1 (2) ................................................................................ 379

Figure 12.2 Watchdog Timer Mode Operation .......................................................................... 387

Figure 12.3 Interval Timer Mode Operation .............................................................................. 388

Figure 12.4 Timing of OVF Setting ........................................................................................... 388

Figure 12.5 Timing of WOVF Setting........................................................................................ 389

Figure 12.6 Writing to TCNT and TCSR (WDT_0)................................................................... 390

Figure 12.7 Writing to RSTCSR ................................................................................................ 391

Figure 12.8 Contention between TCNT Write and Increment.................................................... 392

Section 13 Serial Communication Interface (SCI)

Figure 13.1 Block Diagram of SCI............................................................................................. 396

Figure 13.2 Data Format in Asynchronous Communication (Example with 8-Bit Data, Parity,

Figure 13.3 Receive Data Sampling Timing in Asynchronous Mode ........................................ 427

Figure 13.4 Relationship between Output Clock and Transfer Data Phase

Figure 13.5 Sample SCI Initialization Flowchart ....................................................................... 429

Figure 13.6 Example of Operation in Transmission in Asynchronous Mode

Figure 13.7 Sample Serial Transmission Flowchart ................................................................... 431

Figure 13.8 Example of SCI Operation in Reception

Figure 13.9 Sample Serial Reception Data Flowchart (1) .......................................................... 434

Two Stop Bits) ........................................................................................................ 425

(Asynchronous Mode)............................................................................................. 428

(Example with 8-Bit Data, Parity, One Stop Bit) .................................................... 430

(Example with 8-Bit Data, Parity, One Stop Bit) .................................................... 432

Rev. 6.00 Sep. 24, 2009 Page xxxiii of xlvi

REJ09B0099-0600

Related parts for DF2505BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: