DF2505BR26DV Renesas Electronics America, DF2505BR26DV Datasheet - Page 36

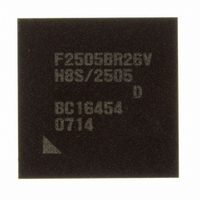

DF2505BR26DV

Manufacturer Part Number

DF2505BR26DV

Description

IC H8S/2505 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2505BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

384KB (384K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2505BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 36 of 980

- Download datasheet (6Mb)

Figure 13.9 Sample Serial Reception Data Flowchart (2) .......................................................... 435

Figure 13.10 Example of Communication Using Multiprocessor Format

Figure 13.11 Sample Multiprocessor Serial Transmission Flowchart.......................................... 439

Figure 13.12 Example of SCI Operation in Reception

Figure 13.13 Sample Multiprocessor Serial Reception Flowchart (1).......................................... 442

Figure 13.13 Sample Multiprocessor Serial Reception Flowchart (2).......................................... 443

Figure 13.14 Data Format in Clocked Synchronous Communication (For LSB-First) ................ 444

Figure 13.15 Sample SCI Initialization Flowchart ....................................................................... 445

Figure 13.16 Sample SCI Transmission Operation in Clocked Synchronous Mode.................... 447

Figure 13.17 Sample Serial Transmission Flowchart................................................................... 448

Figure 13.18 Example of SCI Operation in Reception................................................................. 449

Figure 13.19 Sample Serial Reception Flowchart ........................................................................ 450

Figure 13.20 Sample Flowchart of Simultaneous Serial Transmit and Receive Operations ........ 452

Figure 13.21 (1) Schematic Diagram of Smart Card Interface Pin Connections

Figure 13.21 (2) Schematic Diagram of Smart Card Interface Pin Connections

Figure 13.22 Normal Smart Card Interface Data Format ............................................................. 454

Figure 13.23 Direct Convention (SDIR = SINV = O/E = 0) ........................................................ 455

Figure 13.24 Inverse Convention (SDIR = SINV = O/E = 1) ...................................................... 455

Figure 13.25 Receive Data Sampling Timing in Smart Card Interface Mode

Figure 13.26 Retransfer Operation in SCI Transmit Mode .......................................................... 459

Figure 13.27 TEND Flag Generation Timing in Transmission Operation ................................... 459

Figure 13.28 Example of Transmission Processing Flow ............................................................ 460

Figure 13.29 Retransfer Operation in SCI Receive Mode............................................................ 462

Figure 13.30 Example of Reception Processing Flow.................................................................. 462

Figure 13.31 Timing for Fixing Clock Output Level ................................................................... 463

Figure 13.32 Clock Halt and Restart Procedure ........................................................................... 464

Figure 13.33 Example of Clocked Synchronous Transmission by DTC...................................... 468

Figure 13.34 Sample Flowchart for Mode Transition during Transmission................................. 469

Figure 13.35 Asynchronous Transmission Using Internal Clock................................................. 469

Figure 13.36 Clocked Synchronous Transmission Using Internal Clock..................................... 470

Figure 13.37 Sample Flowchart for Mode Transition during Reception...................................... 471

Figure 13.38 Operation when Switching from SCK Pin to Port Pin ............................................ 472

Figure 13.39 Operation when Switching from SCK Pin to Port Pin

Rev. 6.00 Sep. 24, 2009 Page xxxiv of xlvi

REJ09B0099-0600

(Transmission of Data H'AA to Receiving Station A) ............................................ 437

(Example with 8-Bit Data, Multiprocessor Bit, One Stop Bit) ............................... 441

(Using Clock of 372 Times the Transfer Rate) ....................................................... 457

(Example of Preventing Low-Level Output)........................................................... 473

(Channels 0, 1, 3, and 4) .................................................................................... 453

(Channel 2) ........................................................................................................ 454

Related parts for DF2505BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: