DF2505BR26DV Renesas Electronics America, DF2505BR26DV Datasheet - Page 239

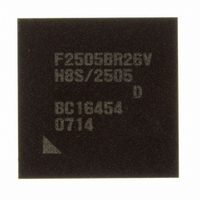

DF2505BR26DV

Manufacturer Part Number

DF2505BR26DV

Description

IC H8S/2505 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2505BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

384KB (384K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2505BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 239 of 980

- Download datasheet (6Mb)

3. Check that the SWDTE bit in DTVECR is 0. Check that there is currently no transfer

4. Write 1 to the SWDTE bit and the vector number (H'60) to DTVECR. The write data is H'E0.

5. Read DTVECR again and check that it is set to the vector number (H'60). If it is not, this

6. If the write was successful, the DTC is activated and a block of 128 bytes of data is

7. After the transfer, an SWDTEND interrupt occurs. The interrupt handling routine should clear

8.8

8.8.1

The DTC operation can be disabled or enabled using the module stop control register. The initial

setting is for the DTC operation to be enabled. Register access is disabled by setting module stop

mode. Module stop mode cannot be set during the DTC operation. For details, see section 22,

Power-Down Modes.

8.8.2

The MRA, MRB, SAR, DAR, CRA, and CRB registers are all located in on-chip RAM. When the

DTC is used, the RAME bit in SYSCR should not be cleared to 0.

8.8.3

For DTCE bit setting, use bit manipulation instructions such as BSET and BCLR for reading and

writing. When multiple activation sources are to be set at one time, only at the initial setting,

writing data is enabled after executing a dummy read on the relevant register with all the interrupts

being masked.

activated by software.

indicates that the write has failed. This is presumably because an interrupt occurred between

steps 3 and 4 and led to a different software activation. To activate this transfer, go back to

step 3.

transferred.

the SWDTE bit to 0 and perform other wrap-up processing.

Usage Notes

Module Stop Mode Setting

On-Chip RAM

DTCE Bit Setting

Rev. 6.00 Sep. 24, 2009 Page 191 of 928

Section 8 Data Transfer Controller (DTC)

REJ09B0099-0600

Related parts for DF2505BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: