DF2505BR26DV Renesas Electronics America, DF2505BR26DV Datasheet - Page 449

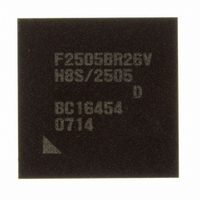

DF2505BR26DV

Manufacturer Part Number

DF2505BR26DV

Description

IC H8S/2505 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2505BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

384KB (384K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2505BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 449 of 980

- Download datasheet (6Mb)

Bit

6

5

4

3

Bit Name

CHR

PE

O/E

STOP

Initial

Value

0

0

0

0

R/W

R/W

R/W

R/W

R/W

Description

0: Selects 8 bits as the data length.

1: Selects 7 bits as the data length. LSB-first is fixed and

In clocked synchronous mode, a fixed data length of 8

bits is used.

Parity Enable (enabled only in asynchronous mode)

When this bit is set to 1, the parity bit is added to transmit

data before transmission, and the parity bit is checked in

reception. For a multiprocessor format, parity bit addition

and checking are not performed regardless of the PE bit

setting.

Parity Mode (enabled only when the PE bit is 1 in

asynchronous mode)

0: Selects even parity.

1: Selects odd parity.

Stop Bit Length (enabled only in asynchronous mode)

Selects the stop bit length in transmission.

0: 1 stop bit

1: 2 stop bits

In reception, only the first stop bit is checked. If the

second stop bit is 0, it is treated as the start bit of the

next transmit character.

Character Length (enabled only in asynchronous mode)

the MSB (bit 7) of TDR is not transmitted in

transmission.

When even parity is set, parity bit addition is

performed in transmission so that the total number of 1

bits in the transmit character plus the parity bit is even.

In reception, a check is performed to see if the total

number of 1 bits in the receive character plus parity bit

is even.

When odd parity is set, parity bit addition is performed

in transmission so that the total number of 1 bits in the

transmit character plus the parity bit is odd. In

reception, a check is performed to see if the total

number of 1 bits in the receive character plus the

parity bit is odd.

Section 13 Serial Communication Interface (SCI)

Rev. 6.00 Sep. 24, 2009 Page 401 of 928

REJ09B0099-0600

Related parts for DF2505BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: