DF2505BR26DV Renesas Electronics America, DF2505BR26DV Datasheet - Page 464

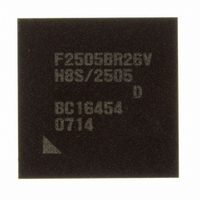

DF2505BR26DV

Manufacturer Part Number

DF2505BR26DV

Description

IC H8S/2505 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2505BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

384KB (384K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2505BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 464 of 980

- Download datasheet (6Mb)

Section 13 Serial Communication Interface (SCI)

Notes: etu: Elementary time unit (time for transfer of 1 bit)

Rev. 6.00 Sep. 24, 2009 Page 416 of 928

REJ09B0099-0600

Bit

2

1

0

1. Only 0 can be written to this bit, to clear the flag.

2. This bit is cleared by DTC only when DISEL is 0 with the transfer counter other than 0.

3. To clear the flag by using the CPU, write 0 to the flag and then read it once again.

Bit Name

TEND

MPB

MPBT

Initial

Value

1

0

0

R/W

R

R

R/W

Description

Transmit End

This bit is set to 1 when no error signal has been sent

back from the receiving end and the next transmit data is

ready to be transferred to TDR.

[Setting conditions]

•

•

The timing of bit setting differs according to the register

setting as follows:

When GM = 0 and BLK = 0, 12.5 etu after transmission

starts

When GM = 0 and BLK = 1, 11.5 etu after transmission

starts

When GM = 1 and BLK = 0, 11.0 etu after transmission

starts

When GM = 1 and BLK = 1, 11.0 etu after transmission

starts

[Clearing conditions]

•

•

Multiprocessor Bit

This bit is not used in Smart Card interface mode.

Multiprocessor Bit Transfer

Write 0 to this bit in Smart Card interface mode.

When the TE bit in SCR is 0 and the ERS bit is also 0

When the ERS bit is 0 and the TDRE bit is 1 after the

specified interval following transmission of 1-byte

data.

When 0 is written to TDRE after reading TDRE = 1

When the DTC*

transfers transmit data to TDR

2

is activated by a TXI interrupt and

Related parts for DF2505BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: