DF2505BR26DV Renesas Electronics America, DF2505BR26DV Datasheet - Page 856

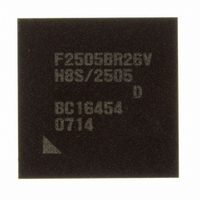

DF2505BR26DV

Manufacturer Part Number

DF2505BR26DV

Description

IC H8S/2505 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2505BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

384KB (384K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2505BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 856 of 980

- Download datasheet (6Mb)

Section 22 Power-Down Modes

22.9

22.9.1

In software standby mode and watch mode, I/O port states are retained. Therefore, there is no

reduction in current consumption for the output current when a high-level signal is output.

22.9.2

Current consumption increases during the oscillation settling wait period.

22.9.3

Depending on the operating status of the DTC, the MSTPA6 bit may not be set to 1. Setting of the

DTC module stop mode should be carried out only when the respective module is not activated.

For details, refer to section 8, Data Transfer Controller (DTC).

22.9.4

• Module stop mode

• Watch mode

22.9.5

MSTPCR should only be written to by the CPU.

Rev. 6.00 Sep. 24, 2009 Page 808 of 928

REJ09B0099-0600

Relevant interrupt operations cannot be performed in module stop mode. Consequently, if

module stop mode is entered when an interrupt has been requested, it will not be possible to

clear the CPU interrupt source or the DTC activation source.

Interrupts should therefore be disabled before entering module stop mode.

On-chip peripheral modules (DTC, TPU, and IIC2) that stop operation in watch mode cannot

clear interrupt sources of the CPU after they make a transition to watch mode while an

interrupt is being requested.

Interrupts should therefore be disabled before executing the SLEEP instruction and entering

watch mode.

Usage Notes

I/O Port Status

Current Consumption during Oscillation Settling Wait Period

DTC Module Stop

On-Chip Peripheral Module Interrupt

Writing to MSTPCR

Related parts for DF2505BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: