HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 158

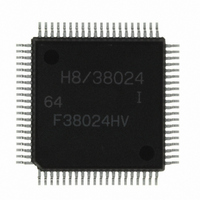

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 158 of 684

- Download datasheet (5Mb)

Section 5 Power-Down Modes

5.5

5.5.1

The system goes from subactive mode to subsleep mode when a SLEEP instruction is executed

while the SSBY bit in SYSCR1 is cleared to 0, LSON bit in SYSCR1 is set to 1, and TMA3 bit in

TMA is set to 1. In subsleep mode, operation of on-chip peripheral modules other than the A/D

converter and PWM is in active state. As long as a minimum required voltage is applied, the

contents of CPU registers, the on-chip RAM and some registers of the on-chip peripheral modules

are retained. I/O ports keep the same states as before the transition.

5.5.2

Subsleep mode is cleared by an interrupt (timer A, timer C, timer F, timer G, asynchronous event

counter, SCI3, IRQAEC, IRQ

pin.

• Clearing by interrupt

• Clearing by RES input

Rev. 8.00 Mar. 09, 2010 Page 136 of 658

REJ09B0042-0800

When an interrupt is requested, subsleep mode is cleared and interrupt exception handling

starts. Subsleep mode is not cleared if the I bit of CCR is set to 1 or the particular interrupt is

disabled in the interrupt enable register.

To synchronize the interrupt request signal with the system clock, up to 2/φ

occur after the interrupt request signal occurrence, before the interrupt exception handling

start.

Clearing by RES pin is the same as for standby mode; see Clearing by RES pin in section

5.3.2, Clearing Standby Mode.

Subsleep Mode

Transition to Subsleep Mode

Clearing Subsleep Mode

4

, IRQ

3

, IRQ

1

, IRQ

0

, WKP

7

to WKP

0

) or by a low input at the RES

SUB

(s) delay may

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: