HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 17

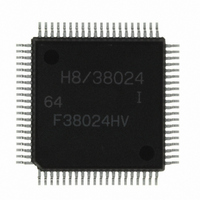

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 17 of 684

- Download datasheet (5Mb)

9.4

9.5

9.6

9.7

Section 10 Serial Communication Interface ......................................................333

10.1 Overview............................................................................................................................ 333

10.2 Register Descriptions ......................................................................................................... 337

9.3.1

9.3.2

9.3.3

9.3.4

Timer F .............................................................................................................................. 263

9.4.1

9.4.2

9.4.3

9.4.4

9.4.5

Timer G.............................................................................................................................. 283

9.5.1

9.5.2

9.5.3

9.5.4

9.5.5

9.5.6

Watchdog Timer ................................................................................................................ 302

9.6.1

9.6.2

9.6.3

9.6.4

Asynchronous Event Counter (AEC) ................................................................................. 313

9.7.1

9.7.2

9.7.3

9.7.4

9.7.5

10.1.1 Features................................................................................................................. 333

10.1.2 Block Diagram ...................................................................................................... 335

10.1.3 Pin Configuration.................................................................................................. 336

10.1.4 Register Configuration.......................................................................................... 336

10.2.1 Receive Shift Register (RSR) ............................................................................... 337

10.2.2 Receive Data Register (RDR) ............................................................................... 337

10.2.3 Transmit Shift Register (TSR) .............................................................................. 338

10.2.4 Transmit Data Register (TDR).............................................................................. 338

Overview............................................................................................................... 255

Register Descriptions ............................................................................................ 257

Timer Operation.................................................................................................... 260

Timer C Operation States...................................................................................... 262

Overview............................................................................................................... 263

Register Descriptions ............................................................................................ 266

CPU Interface ....................................................................................................... 273

Operation .............................................................................................................. 276

Application Notes ................................................................................................. 279

Overview............................................................................................................... 283

Register Descriptions ............................................................................................ 285

Noise Canceler ...................................................................................................... 290

Operation .............................................................................................................. 292

Application Notes ................................................................................................. 297

Timer G Application Example .............................................................................. 301

Overview............................................................................................................... 302

Register Descriptions ............................................................................................ 305

Timer Operation.................................................................................................... 311

Watchdog Timer Operation States ........................................................................ 312

Overview............................................................................................................... 313

Register Configurations ........................................................................................ 316

Operation .............................................................................................................. 325

Asynchronous Event Counter Operation Modes................................................... 330

Application Notes ................................................................................................. 330

Rev. 8.00 Mar. 09, 2010 Page xv of xx

REJ09B0042-0800

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: