HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 364

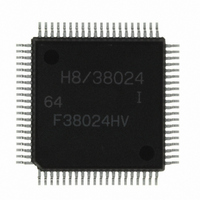

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 364 of 684

- Download datasheet (5Mb)

Section 10 Serial Communication Interface

Bits 1 and 0—Clock Select 1, 0 (CKS1, CKS0)

Bits 1 and 0 choose φ/64, φ/16, φw/2, or φ as the clock source for the baud rate generator.

For the relation between the clock source, bit rate register setting, and baud rate, see section

10.2.8, Bit rate register (BRR).

Bit 1

CKS1

0

0

1

1

Notes: 1. φ w/2 clock in active (medium-speed/high-speed) mode and sleep mode

10.2.6

SCR3 is an 8-bit register for selecting transmit or receive operation, the asynchronous mode clock

output, interrupt request enabling or disabling, and the transmit/receive clock source.

SCR3 can be read or written by the CPU at any time.

SCR3 is initialized to H'00 upon reset, and in standby, module standby or watch mode.

Bit 7—Transmit Interrupt Enable (TIE)

Bit 7 selects enabling or disabling of the transmit data empty interrupt request (TXI) when

transmit data is transferred from the transmit data register (TDR) to the transmit shift register

(TSR), and bit TDRE in the serial status register (SSR) is set to 1.

TXI can be released by clearing bit TDRE or bit TIE to 0.

Rev. 8.00 Mar. 09, 2010 Page 342 of 658

REJ09B0042-0800

Bit

Initial value

Read/Write

2. φ w clock in subactive mode and subsleep mode. In subactive or subsleep mode, SCI3

Serial Control Register 3 (SCR3)

can be operated when CPU clock is φw/2 only.

Bit 0

CKS0

0

1

0

1

R/W

TIE

7

0

Description

φ clock

φ w/2 clock *

φ/16 clock

φ/64 clock

R/W

RIE

6

0

1

/φ w clock *

R/W

TE

5

0

2

R/W

RE

4

0

MPIE

R/W

3

0

TEIE

R/W

2

0

CKE1

R/W

1

0

(initial value)

CKE0

R/W

0

0

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: