HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 563

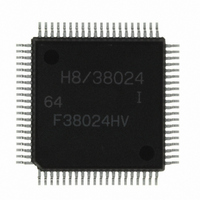

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 563 of 684

- Download datasheet (5Mb)

A.3

The tables here can be used to calculate the number of states required for instruction execution.

Table A.4 indicates the number of states required for each cycle (instruction fetch, read/write,

etc.), and table A.3 indicates the number of cycles of each type occurring in each instruction. The

total number of states required for execution of an instruction can be calculated from these two

tables as follows:

Execution states = I × S

Examples: When instruction is fetched from on-chip ROM, and an on-chip RAM is accessed.

BSET #0, @FF00

From table A.4:

I = L = 2,

From table A.3:

S

Number of states required for execution = 2 × 2 + 2 × 2 = 8

When instruction is fetched from on-chip ROM, branch address is read from on-chip ROM, and

on-chip RAM is used for stack area.

JSR @@ 30

From table A.4:

I = 2,

From table A.3:

S

Number of states required for execution = 2 × 2 + 1 × 2+ 1 × 2 = 8

Table A.3

Execution Status

(instruction cycle)

Instruction fetch

Branch address read

Stack operation

Byte data access

Word data access

Internal operation

Note: * Depends on which on-chip module is accessed. See section 2.9.1, Notes on Data Access

I

I

= 2,

= S

J

= S

J = K = 1,

for details.

S

Number of Execution States

K

L

= 2

= 2

J = K = M = N= 0

Number of Cycles in Each Instruction

L = M = N = 0

I

+ J × S

S

S

S

S

S

S

I

J

K

L

M

N

J

+ K × S

On-Chip Memory

2

1

K

+ L × S

L

+ M × S

Rev. 8.00 Mar. 09, 2010 Page 541 of 658

Access Location

M

+ N × S

On-Chip Peripheral Module

—

2 or 3 *

—

Appendix A CPU Instruction Set

N

REJ09B0042-0800

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: