HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 42

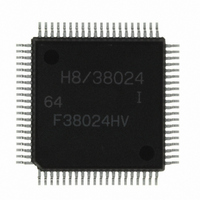

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 42 of 684

- Download datasheet (5Mb)

Section 1 Overview

Type

Clock

pins

System

control

Interrupt

pins

Rev. 8.00 Mar. 09, 2010 Page 20 of 658

REJ09B0042-0800

Symbol

OSC

OSC

X

X

RES

TEST

IRQ

IRQ

IRQ

IRQ

IRQAEC 60

1

2

0

1

3

4

1

2

FP-80A

TFP-80C FP-80B TLP-85V

10

9

6

7

12

11

72

76

5

3

12

11

8

9

14

13

74

78

7

5

62

Pin No.

F2

E3

D3

D2

F3

E2

C5

B3

D1

B2

C10

Pad

No. *

11

10

6

7

13

12

73

77

5

3

61

1

Pad

No. *

12

11

7

8

14

13

74

78

6

4

62

2

Pad

No. *

10

9

6

7

12

11

72

76

5

3

60

3

I/O

Input

Output

Input

Output

Input

Input

Input

Input

Name and Functions

These pins connect to a

crystal or ceramic

oscillator, or can be used

to input an external clock.

See section 4, Clock

Pulse Generators, for a

typical connection

diagram.

These pins connect to a

32.768-kHz or 38.4-kHz *

crystal oscillator.

See section 4, Clock

Pulse Generators, for a

typical connection

diagram.

Reset: When this pin is

driven low, the chip is

reset

Test pin: This pin is

reserved and cannot be

used. It should be

connected to V

IRQ interrupt request 0,

1, 3, and 4: These are

input pins for edge-

sensitive external

interrupts, with a selection

of rising or falling edge

Asynchronous event

counter event signal:

This is an interrupt input

pin for enabling

asynchronous event

input.

On the H8/38124 Group,

this must be fixed at V

or GND because the

oscillator is selected by

the input level during

resets. Refer to section 4,

Clock Pulse Generators,

for information on the

selection method.

SS

.

CC

5

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: