HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 64

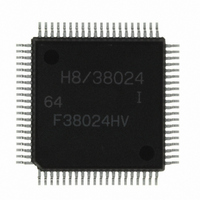

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 64 of 684

- Download datasheet (5Mb)

Section 2 CPU

2.5.2

Table 2.5 describes the arithmetic instructions.

Table 2.5

Instruction

ADD

SUB

ADDX

SUBX

INC

DEC

ADDS

SUBS

DAA

DAS

MULXU

DIVXU

CMP

NEG

Note:

Rev. 8.00 Mar. 09, 2010 Page 42 of 658

REJ09B0042-0800

* Size: Operand size

Arithmetic Operations

B:

W:

Arithmetic Instructions

Byte

Word

Size *

B/W

B

B

W

B

B

B

B/W

B

Function

Rd ± Rs → Rd, Rd + #IMM → Rd

Performs addition or subtraction on data in two general registers,

or addition on immediate data and data in a general register.

Immediate data cannot be subtracted from data in a general

register. Word data can be added or subtracted only when both

words are in general registers.

Rd ± Rs ± C → Rd, Rd ± #IMM ± C → Rd

Performs addition or subtraction with carry or borrow on byte data

in two general registers, or addition or subtraction on immediate

data and data in a general register.

Rd ± 1 → Rd

Increments or decrements a general register by 1.

Rd ± 1 → Rd, Rd ± 2 → Rd

Adds or subtracts 1 or 2 to or from a general register

Rd decimal adjust → Rd

Decimal-adjusts (adjusts to 4-bit BCD) an addition or subtraction

result in a general register by referring to the CCR

Rd × Rs → Rd

Performs 8-bit × 8-bit unsigned multiplication on data in two

general registers, providing a 16-bit result

Rd ÷ Rs → Rd

Performs 16-bit ÷ 8-bit unsigned division on data in two general

registers, providing an 8-bit quotient and 8-bit remainder

Rd – Rs, Rd – #IMM

Compares data in a general register with data in another general

register or with immediate data, and indicates the result in the

CCR. Word data can be compared only between two general

registers.

0 – Rd → Rd

Obtains the two’s complement (arithmetic complement) of data in a

general register

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: