HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 462

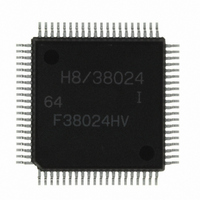

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 462 of 684

- Download datasheet (5Mb)

Section 14 Power-On Reset and Low-Voltage Detection Circuits (H8/38124 Group Only)

14.3.2

LVDR (Reset by Low Voltage Detect) Circuit:

Figure 14.3 shows the timing of the LVDR function. The LVDR enters the module-standby state

after a power-on reset is canceled. To operate the LVDR, set the LVDE bit in LVDCR to 1, wait

for 150 μs (t

stabilized, based on overflow of LVDNT, etc., then set the LVDRE bit in LVDCR to 1. After that,

the output settings of ports must be made. To cancel the low-voltage detection circuit, first the

LVDRE bit should be cleared to 0 and then the LVDE bit should be cleared to 0. The LVDE and

LVDRE bits must not be cleared to 0 simultaneously because incorrect operation may occur.

When the power-supply voltage falls below the Vreset voltage (typ. = 2.3 V or 3.3 V), the LVDR

clears the LVDRES signal to 0, and resets the prescaler S. The low-voltage detection reset state

remains in place until a power-on reset is generated. When the power-supply voltage rises above

the Vreset voltage again, the prescaler S starts counting. It counts 131,072 clock (φ) cycles, and

then releases the internal reset signal. In this case, the LVDE, LVDSEL, and LVDRE bits in

LVDCR are not initialized.

Note that if the power supply voltage (Vcc) falls below V

point, the low-voltage detection reset may not occur.

If the power supply voltage (Vcc) falls below Vpor = 100 mV, a power-on reset occurs.

Rev. 8.00 Mar. 09, 2010 Page 440 of 658

REJ09B0042-0800

RES

Vcc

PSS-reset

signal

OVF

Internal reset

signal

Low-Voltage Detection Circuit

LVDON

Vpor

t

PWON

Figure 14.2 Operational Timing of Power-On Reset Circuit

) until the reference voltage and the low-voltage-detection power supply have

PSS counter starts

131,072 cycles

Reset released

LVDRmin

= 1.0 V and then rises from that

Vss

Vss

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: