tdat04622 ETC-unknow, tdat04622 Datasheet - Page 75

tdat04622

Manufacturer Part Number

tdat04622

Description

Tdat Sonet/sdh 155/622/2488 Mbits/s Data Interfaces

Manufacturer

ETC-unknow

Datasheet

1.TDAT04622.pdf

(310 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 75 of 310

- Download datasheet (3Mb)

Data Sheet

May 2001

Agere Systems Inc.

Overview

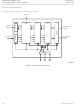

When used to implement a POS UNI, the device writes packets into an internal 256-byte FIFO buffer using a

generic 8-/16-/32-bit wide enhanced UTOPIA 2/3 compliant interface. HDLC framing performs the insertion of

flags, control escape characters, and the FCS fields. Either the CRC-ITU or CRC-32 (in regular or reversed mode)

can be computed and added to the frame. Counts of transmitted packets and errored/dropped packets are accu-

mulated for performance monitoring purposes.

ATM/HDLC/HDLC-CRC/PPP Support

TDAT042G5 supports the transfer of ATM cells or variable-length packets. Support for 52- or 53-byte cell sizes is

provided at the UTOPIA interface through register provisioning. The following three types of packet data can be

sent and received with HLDC-like framing: transparent HDLC, CRC, and PPP. Transparent HDLC contains 0x7E

framing but no CRC. CRC mode is HDLC with an attached CRC. PPP has 0x7E framing with provisionable

attached header information and CRC.

When used to implement an ATM UNI, the device performs cell delineation on the SPE. HEC error correction is

provided. Idle/unassigned cells may be dropped according to a programmable filter. Cells are also dropped upon

detection of an uncorrectable header check sequence error. The ATM cell payloads are descrambled before being

passed to a 4-cell FIFO buffer. The received cells are read from the FIFO using a generic 8-/16-/32-bit wide

UTOPIA 2/3 compliant interface. Counts of received ATM cells, uncorrectable HEC errors, and correctable HEC

errors are accumulated independently for performance monitoring purposes.

When used to implement a POS UNI, the device descrambles the SPE before extracting HDLC frames. The con-

trol escape characters are removed. Descrambling can be performed after control escape byte destuffing (or

before to control malicious HDLC expansion)

rectness. The packets are placed into a 256-byte FIFO buffer.* The received packets are read from the FIFO using

a generic 8-/16-/32-bit wide enhanced UTOPIA 2/3 compliant interface. Counts of received packets and errored/

dropped packets are accumulated independently for performance monitoring purposes. The device POS imple-

mentation also allows the optional attach/detach of a per-channel provisionable PPP header.

* FIFOs are 256 bytes per channel and cannot be reallocated.

(continued)

.

The optional 16- or 32-bit error check sequence is verified for cor-

155/622/2488 Mbits/s Data Interface

TDAT042G5 SONET/SDH

47

Related parts for tdat04622

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

ETC-unknow

Datasheet:

Part Number:

Description:

Manufacturer:

ETC-unknow

Datasheet: