tdat04622 ETC-unknow, tdat04622 Datasheet - Page 79

tdat04622

Manufacturer Part Number

tdat04622

Description

Tdat Sonet/sdh 155/622/2488 Mbits/s Data Interfaces

Manufacturer

ETC-unknow

Datasheet

1.TDAT04622.pdf

(310 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 79 of 310

- Download datasheet (3Mb)

Data Sheet

May 2001

Agere Systems Inc.

Functional Description

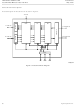

Line Interface Block

This device is designed to work with commonly available optoelectronic converters for OC-3, OC-12, and OC-48

line rates. It will also work with available multiplexer and demultiplexer chip sets for an STS-48/STM-16 line inter-

face rate. The line interface will operate in one of three possible modes, and is provisioned through core register

0x0010 (mode), bits 4—0. These three values of the mode register are the only values allowed.

Table 12. Line Interface Modes

This block provides the interface between the external SONET/SDH line components and the overhead processor

(OHP) block. The line interface must provide transmit/receive functions for quad STS-3/STM-1, quad STS-12/

STM-4, and STS-48/STM-16 applications. All external inputs and outputs for the TDAT042G5 line I/O block are ref-

erenced to the positive edge of the clock. When the external devices are referenced to the negative edge, the dif-

ferential input clock will need to be reversed at the TDAT042G5 input.

Receive Line Interface Summary

The following list summarizes the receive line interface operations for each STS mode:

I

I

I

I

I

In quad STS-3/STM-1 mode, the receive line interface provides four separate STS-3/STM-1 input pin groups.

Each input group comprises a differential LVPECL 155.52 Mbits/s data input and a differential 155.52 MHz clock.

Each input group provides data to only one of four (A, B, C, or D) OHP blocks. This interface is synchronous and

requires an external CDR.

In quad STS-12/STM-4 mode, the receive line interface provides four separate STS-12/STM-4 input pin groups.

Each input group comprises a differential LVPECL 622.08 Mbits/s data input and a differential 622.08 MHz clock.

Each input group provides data to only one of four (A, B, C, or D) OHP blocks. This interface is synchronous and

requires an external CDR.

In the STS-48/STM-16 mode, the device provides 16 differential LVPECL data inputs at 155.52 Mbits/s with a dif-

ferential LVPECL 155.52 MHz clock. In this mode, an external 1:16 data demultiplexer with a 1/16 clock divider is

required. External barrel shifter circuitry to byte align the data is not required.

Multiplexers select between the terminal loopback data, the 32-bit parallel STS-48/STM-16 data bus, and the

four STS-12/STM-4 or STS-3/STM-1 8-bit parallel data buses. The controls for these MUXes are mode (register

0x0010) and loopback (register 0x0012) provided by the control block (see Table 48 and Table 50 on pages

150—151).

For STS-48 mode, the 155.52 MHz input clock is divided by two to 77.76 MHz and distributed to all four multi-

plexers. For the STS-12/STM-4 mode, each 622.08 MHz input clock is divided by eight to 77.76 MHz. Each

77.76 MHz clock is distributed to the appropriate clock multiplexer (A, B, C, or D). For the STS-3/STM-1 mode,

each 155.52 MHz input clock is divided by eight to 19.44 MHz. Each 19.44 MHz clock is distributed to the appro-

priate clock multiplexer (A, B, C, or D).

Core Register

Mode[4:0]

0x0010

10000

01111

00000

STS-48/STM-16

STS-12/STM-4

STS-3/STM-1

Interfaces

(continued)

RxCKP/N, RxD[15:0]P/N, TxCKP/N, TxD[15:0]P/N

RxCLK[D]P/N, RxD[D]P/N, TxCKP/N, TxD[D]P/N

RxCLK[C]P/N, RxD[C]P/N, TxCKP/N, TxD[C]P/N

RxCLK[B]P/N, RxD[B]P/N, TxCKP/N, TxD[B]P/N

RxCLK[A]P/N, RxD[A]P/N, TxCKP/N, TxD[A]P/N

RxCLK[D]P/N, RxD[DP/N, TxCKP/N, TxD[D]P/N

RxCLK[C]P/N, RxD[C]P/N, TxCKP/N, TxD[C]P/N

RxCLK[B]P/N, RxD[B]P/N, TxCKP/N, TxD[B]P/N

RxCLK[A]P/N, RxD[A]P/N, TxCKP/N, TxD[A]P/N

Line Interface Signals

155/622/2488 Mbits/s Data Interface

TDAT042G5 SONET/SDH

51

Related parts for tdat04622

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

ETC-unknow

Datasheet:

Part Number:

Description:

Manufacturer:

ETC-unknow

Datasheet: