tdat04622 ETC-unknow, tdat04622 Datasheet - Page 80

tdat04622

Manufacturer Part Number

tdat04622

Description

Tdat Sonet/sdh 155/622/2488 Mbits/s Data Interfaces

Manufacturer

ETC-unknow

Datasheet

1.TDAT04622.pdf

(310 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 80 of 310

- Download datasheet (3Mb)

TDAT042G5 SONET/SDH

155/622/2488 Mbits/s Data Interface

Functional Description

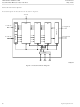

Line Interface Block

Transmit Line Interface Summary

The following list summarizes the transmit line interface operations for each STS mode.

I

I

I

Table 13. Clock Settings for CLKDIV Pin

I

I

I

Line interface timing is given in the Interface Timing Specifications section (see Table 168, page 267).

* Contra refers to a type of data transmission whereby a clock signal is received by a register before the register sends data.

52

In the STS-48/STM-16 case, two transmit clock modes are available, contra* and forward clocking. In the contra-

clocking mode, the transmit data is sent out as commanded by TxCKP/N; in addition, an internal PLL must be

activated, core register 0x0010 bit 5, to minimize the phase delay between TxCKP/N and the transmitted data. In

the forward clocking mode, the transmit data and the clock, TxCKQ (used to clock out the data), are sent in par-

allel to the transmit multiplexer.

In STS-12/STM-4 and STS-3/STM-1 modes, the input clock is divided by eight producing the internal clock at

77.76 MHz and 19.44 MHz, respectively. In STS-48/STM-16 mode, the input clock is divided by eight to produce

an internal clock at 77.76 MHz. The CLKDIV pin (H4) controls this division. Table 13 shows the required value of

CLKDIV.

In quad STS-3/STM-1 and STS-12/STM-4 modes, the transmit line interface receives 8 bits of data from each

OHP block (A, B, C, and D) at 19.44 Mbits/s and 77.76 Mbits/s, respectively. An 8-to-1 parallel-to-serial conver-

sion produces output data at 155.52 Mbits/s for STS-3/STM-1 mode and 622.08 Mbits/s for STS-12/STM-4

mode. For facility loopback, the outputs are multiplexed with the corresponding data from the STS-12/STS-3

(STM-4/STM-1) receive block and sent to four differential LVPECL buffers.

In STS-48/STM-16 mode, a 32-bit data word at 77.76 Mbits/s is received from the OH P. Then a 2-to-1 parallel-to-

parallel conversion is performed producing a 16-bit word at 155.52 Mbits/s. In this mode, an external 16:1 data

demultiplexer is required. Facility loopback is not available for the STS-48/STM-16 mode.

There is a single clock input, TxCKP/N, in the transmit case. The clock source rates are 622.08 MHz (STS-12/

STM-4), 155.52 MHz (STS-3/STM-1), or 155.52 MHz (STS-48/STM-16).

TxFSYNCP/N is an optional external frame sync. This 8 kHz frame sync pulse must be synchronous with

TxCKP/N. It is, at minimum, a one TxCKP/N clock cycle wide pulse that is latched in at the system rate

(622.08 MHz or 155.52 MHz). TOH interface signal RxREF should not be used as a source to TxFSYNCP/N.

The active edge of the transmit clock is the positive edge.

When TDAT042G5 operates in asynchronous mode (MPMODE = 0), the line block provides the microprocessor

clock to the microprocessor interface block. The CLKDIV pin must be set to ensure that the clock is always

77.76 MHz.

CLKDIV Pin

CLKDIV = 1

CLKDIV = 0

When in STS-12/STM-4 (622.08 MHz divide by 8).

When in STS-3/STM-1, STS-48/STM-16 (155.52 MHz divide by 2).

(continued)

(continued)

Description

Agere Systems Inc.

Data Sheet

May 2001

Related parts for tdat04622

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

ETC-unknow

Datasheet:

Part Number:

Description:

Manufacturer:

ETC-unknow

Datasheet: