MPC564MZP66 Freescale Semiconductor, MPC564MZP66 Datasheet - Page 667

MPC564MZP66

Manufacturer Part Number

MPC564MZP66

Description

IC MCU 512K FLASH 66MHZ 388-BGA

Manufacturer

Freescale Semiconductor

Series

MPC5xxr

Specifications of MPC564MZP66

Core Processor

PowerPC

Core Size

32-Bit

Speed

66MHz

Connectivity

CAN, EBI/EMI, SCI, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

56

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

2.5 V ~ 2.7 V

Data Converters

A/D 32x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 125°C

Package / Case

388-BGA

For Use With

MPC564EVB - KIT EVAL FOR MPC561/562/563/564

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC564MZP66

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MPC564MZP66R2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 667 of 1420

- Download datasheet (11Mb)

Freescale Semiconductor

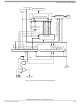

Bits

0:6

10

11

SRESET

7

8

9

Field

Addr

Name

TDRE

RDRF

IDLE

RAF

MSB

TC

—

0

1

Reserved

Transmit data register empty. TDRE is set when the byte in TDRx is transferred to the transmit

serial shifter. If this bit is zero, the transfer is yet to occur and a write to TDRx will overwrite the

previous value. New data is not transmitted if TDRx is written without first clearing TDRE.

0 Transmit data register still contains data to be sent to the transmit serial shifter.

1 A new character can now be written to the transmit data register.

For transmit queue operation, this bit should be ignored by software.

Transmit complete. TC is set when the transmitter finishes shifting out all data, queued preambles

(mark/idle-line), or queued breaks (logic zero).

0 SCI transmitter is busy.

1 SCI transmitter is idle.

For transmit queue operation, TC is cleared when SCxSR is read with TC set, followed by a write

to SCTQ[0:15].

Receive data register full. RDRF is set when the contents of the receive serial shifter are

transferred to register RDRx. If one or more errors are detected in the received word, the

appropriate flag(s) (NF, FE, or PF) are set within the same clock cycle.

0 Receive data register is empty or contains previously read data.

1 Receive data register contains new data.

For receiver queue operation, this bit should be ignored by software.

Receiver active flag. RAF indicates whether the receiver is busy. This flag is set when the receiver

detects a possible start bit and is cleared when the chosen type of idle line is detected. RAF can

be used to reduce collisions in systems with multiple masters.

0 SCI receiver is idle.

1 SCI receiver is busy.

Idle line detected. IDLE is set when the receiver detects an idle-line condition (reception of a

minimum of 10 or 11 consecutive ones as specified by ILT in SCCxR1). This bit is not set by the

idle-line condition when RWU in SCCxR1 is set. Once cleared, IDLE is not set again until after

RDRF is set (after the line is active and becomes idle again). If a break is received, RDRF is set,

allowing a subsequent idle line to be detected again.

Under certain conditions, the IDLE flag may be set immediately following the negation of RE in

SCCxR1. System designs should ensure this causes no detrimental effects.

0 SCI receiver did not detect an idle-line condition.

1 SCI receiver detected an idle-line condition.

For receiver queue operation, IDLE is cleared when SCxSR is read with IDLE set, followed by a

read of SCRQ[0:15].

2

0000_000

—

Figure 15-28. SCIx Status Register (SCxSR)

3

MPC561/MPC563 Reference Manual, Rev. 1.2

Table 15-26. SCxSR Bit Descriptions

4

5

6

0x30 500C; 0x30 5024

TDRE

1

7

Description

TC

1

8

RDRF RAF IDLE

0

9

10

0

Queued Serial Multi-Channel Module

11

0

OR

12

0

NF

13

0

FE

14

0

LSB

PF

15

0

15-49

Related parts for MPC564MZP66

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

MPC5 1K0 5%

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

MPC5 500R 5%

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

MPC5 5K0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 5R0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 50K 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

MPC5 1R0 5%

Manufacturer:

Tyco Electronics

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: