UPD78F1152AGC-GAD-AX Renesas Electronics America, UPD78F1152AGC-GAD-AX Datasheet - Page 101

UPD78F1152AGC-GAD-AX

Manufacturer Part Number

UPD78F1152AGC-GAD-AX

Description

MCU 16BIT 78K0R/KX3 80-LQFP

Manufacturer

Renesas Electronics America

Series

78K0R/Kx3r

Datasheet

1.UPD78F1152AGC-GAD-AX.pdf

(908 pages)

Specifications of UPD78F1152AGC-GAD-AX

Core Processor

78K/0R

Core Size

16-Bit

Speed

20MHz

Connectivity

3-Wire SIO, I²C, LIN, UART/USART

Peripherals

DMA, LVD, POR, PWM, WDT

Number Of I /o

65

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b, D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPD78F1152AGC-GAD-AX

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 101 of 908

- Download datasheet (6Mb)

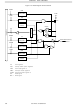

4.2.1 Port 0

using port mode register 0 (PM0). When the P00 to P06 pins are used as an input port, use of an on-chip pull-up

resistor can be specified in 1-bit units by pull-up resistor option register 0 (PU0).

using port input mode register 0 (PIM0).

port output mode register 0 (POM0).

Port 0 is a 7-bit I/O port with an output latch. Port 0 can be set to the input mode or output mode in 1-bit units

Input to the P03 and P04 pins can be specified through a normal input buffer or a TTL input buffer in 1-bit units

Output from the P02 to P04 pins can be specified as N-ch open-drain output (V

This port can also be used for timer I/O, serial interface data I/O, and clock I/O.

Reset signal generation sets port 0 to input mode.

Figures 4-2 to 4-6 show block diagrams of port 0.

Cautions 1. To use P01/TO00, P05/TI05/TO05, or P06/TI06/TO06 as a general-purpose port, set bits 0, 5, 6

P0:

PU0:

PM0:

RD:

WR××: Write signal

2. To use P02/SO10/TxD1, P03/SI10/RxD1/SDA10, or P04/SCK10/SCL10 as a general-purpose

WR

(TO00, TO05, TO06) of timer output register 0 (TO0) and bits 0, 5, 6 (TOE00, TOE05, TOE06) of

timer output enable register 0 (TOE0) to “0”, which is the same as their default status setting.

port, note the serial array unit 0 setting. For details, refer to the following tables.

WR

WR

• Table 12-7 Relationship Between Register Settings and Pins (Channel 2 of Unit 0: CSI10,

• Table 12-8 Relationship Between Register Settings and Pins (Channel 3 of Unit 0: UART1

Read signal

RD

Port register 0

Pull-up resistor option register 0

Port mode register 0

PORT

UART1 Transmission, IIC10)

Reception)

PU

PM

Output latch

Alternate

function

PM00

PU00

(P00)

PU0

PM0

P0

Figure 4-2. Block Diagram of P00

CHAPTER 4 PORT FUNCTIONS

User’s Manual U17893EJ8V0UD

DD

tolerance) in 1-bit units using

EV

DD

P-ch

P00/TI00

99

Related parts for UPD78F1152AGC-GAD-AX

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: