r5f71374an80fpv Renesas Electronics Corporation., r5f71374an80fpv Datasheet - Page 210

r5f71374an80fpv

Manufacturer Part Number

r5f71374an80fpv

Description

32-bit Risc Microcomputer Superh?? Risc Engine Family

Manufacturer

Renesas Electronics Corporation.

Datasheet

1.R5F71374AN80FPV.pdf

(1154 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R5F71374AN80FPV

Manufacturer:

TI

Quantity:

1 001

- Current page: 210 of 1154

- Download datasheet (7Mb)

Section 8 Data Transfer Controller (DTC)

8.5.5

In block transfer mode, data are transferred in block units in response to a single activation

request. Either the transfer source or the transfer destination is designated as a block area by the

DTS bit in MRB.

The block size is 1 to 256 bytes (1 to 256 words, or 1 to 256 longwords). When the block data

transfer of one block ends, the block size counter (CRAL) and address register (SAR when DTS =

1 or DAR when DTS = 0) specified as the block area is restored to the initial state. The other

address register is then incremented, decremented, or left fixed. From 1 to 65,536 transfers can be

specified. When the specified number of transfers ends, an interrupt is requested to the CPU.

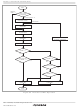

Table 8.8 lists the register function in block transfer mode. Figure 8.8 shows the memory map in

block transfer mode.

Table 8.8

Note:

Rev. 1.00 Sep. 21, 2007 Page 184 of 1124

REJ09B0402-0100

Register Function

SAR

DAR

CRAH

CRAL

CRB

*

Block Transfer Mode

Source address

Destination address

Block size storage

Block size counter

Block transfer counter

Transfer information writeback is skipped.

Register Function in Block Transfer Mode

Written Back Value

DTS = 0: Incremented/decremented/fixed*

DTS = 1: SAR initial value

DTS = 0: DAR initial value

DTS = 1: Incremented/decremented/fixed*

CRAH

CRAH

CRB − 1

Related parts for r5f71374an80fpv

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Renesas Technology Corp [Renesas 32-Bit RISC Microcomputer Super RISC engine Family/SH7700 Series]

Manufacturer:

Renesas Electronics Corporation.

Datasheet:

Part Number:

Description:

RENESAS MCU M16C FAMILY / M16C/Tiny SERIES

Manufacturer:

Renesas Electronics Corporation.

Datasheet:

Part Number:

Description:

Renesas Starter Kit for RX210

Manufacturer:

Renesas Electronics Corporation.

Part Number:

Description:

EVALBOARD/Renesas StarterKit for RX630

Manufacturer:

Renesas Electronics Corporation.

Part Number:

Description:

EVALBOARD/Renesas Starter Kit+ for RX63N

Manufacturer:

Renesas Electronics Corporation.

Part Number:

Description:

EVALBOARD/Renesas Starter Kit

Manufacturer:

Renesas Electronics Corporation.

Part Number:

Description:

FLASH PROGRAMMER FOR RENESAS MICROCONTROLLERS

Manufacturer:

Renesas Electronics Corporation.

Part Number:

Description:

Manufacturer:

Renesas Electronics Corporation.

Datasheet:

Part Number:

Description:

Manufacturer:

Renesas Electronics Corporation.

Datasheet:

Part Number:

Description:

Manufacturer:

Renesas Electronics Corporation.

Datasheet:

Part Number:

Description:

Manufacturer:

Renesas Electronics Corporation.

Datasheet:

Part Number:

Description:

Manufacturer:

Renesas Electronics Corporation.

Datasheet:

Part Number:

Description:

Manufacturer:

Renesas Electronics Corporation.

Datasheet:

Part Number:

Description:

Manufacturer:

Renesas Electronics Corporation.

Datasheet:

Part Number:

Description:

Manufacturer:

Renesas Electronics Corporation.

Datasheet: