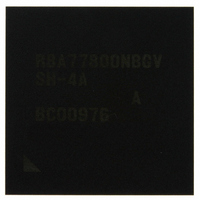

R8A77800ANBGAV Renesas Electronics America, R8A77800ANBGAV Datasheet - Page 14

R8A77800ANBGAV

Manufacturer Part Number

R8A77800ANBGAV

Description

IC SUPERH MPU ROMLESS 449-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77800ANBGV.pdf

(1342 pages)

Specifications of R8A77800ANBGAV

Core Processor

SH-4A

Core Size

32-Bit

Speed

400MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

75

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

1.15 V ~ 1.35 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

449-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77800ANBGAV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 14 of 1342

- Download datasheet (7Mb)

Section 8 Caches................................................................................................ 197

8.1

8.2

8.3

8.4

8.5

8.6

8.7

8.8

Section 9 L Memory.......................................................................................... 227

9.1

9.2

Rev.1.00 Dec. 13, 2005 Page xii of l

7.7.5

7.7.6

Features.............................................................................................................................. 197

Register Descriptions......................................................................................................... 200

8.2.1

8.2.2

8.2.3

8.2.4

Operand Cache Operation.................................................................................................. 207

8.3.1

8.3.2

8.3.3

8.3.4

8.3.5

8.3.6

Instruction Cache Operation .............................................................................................. 212

8.4.1

8.4.2

8.4.3

Cache Operation Instruction .............................................................................................. 214

8.5.1

8.5.2

Memory-Mapped Cache Configuration ............................................................................. 216

8.6.1

8.6.2

8.6.3

8.6.4

Store Queues ...................................................................................................................... 223

8.7.1

8.7.2

8.7.3

8.7.4

8.7.5

Notes on Using 32-Bit Address Extended Mode ............................................................... 226

Features.............................................................................................................................. 227

Register Descriptions......................................................................................................... 228

Memory-Mapped PMB Configuration.................................................................. 192

Notes on Using 32-Bit Address Extended Mode .................................................. 194

Cache Control Register (CCR) ............................................................................. 201

Queue Address Control Register 0 (QACR0)....................................................... 203

Queue Address Control Register 1 (QACR1)....................................................... 204

On-Chip Memory Control Register (RAMCR) .................................................... 205

Read Operation ..................................................................................................... 207

Prefetch Operation ................................................................................................ 208

Write Operation .................................................................................................... 209

Write-Back Buffer ................................................................................................ 211

Write-Through Buffer........................................................................................... 211

OC Two-Way Mode ............................................................................................. 211

Read Operation ..................................................................................................... 212

Prefetch Operation ................................................................................................ 213

IC Two-Way Mode............................................................................................... 213

Coherency between Cache and External Memory ................................................ 214

Prefetch Operation ................................................................................................ 215

IC Address Array.................................................................................................. 217

IC Data Array ....................................................................................................... 219

OC Address Array ................................................................................................ 220

OC Data Array...................................................................................................... 222

SQ Configuration.................................................................................................. 223

Writing to SQ........................................................................................................ 223

Transfer to External Memory ............................................................................... 224

Determination of SQ Access Exception................................................................ 225

Reading from SQ .................................................................................................. 225

Related parts for R8A77800ANBGAV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: