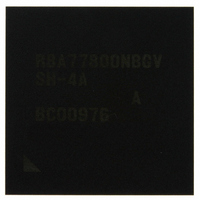

R8A77800ANBGAV Renesas Electronics America, R8A77800ANBGAV Datasheet - Page 42

R8A77800ANBGAV

Manufacturer Part Number

R8A77800ANBGAV

Description

IC SUPERH MPU ROMLESS 449-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77800ANBGV.pdf

(1342 pages)

Specifications of R8A77800ANBGAV

Core Processor

SH-4A

Core Size

32-Bit

Speed

400MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

75

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

1.15 V ~ 1.35 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

449-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77800ANBGAV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 42 of 1342

- Download datasheet (7Mb)

Figure 27.7 Sector Access when Unusable Sector Exists in Continuous Sectors..................... 1048

Figure 27.8 NAND Flash Command Access (Block Erase)..................................................... 1050

Figure 27.9 NAND Flash Sector Access (Flash Write) Using DMA ....................................... 1051

Figure 27.10 NAND Flash Command Access (Flash Read) .................................................... 1052

Section 28 General Purpose I/O (GPIO)

Figure 28.1 Port Data Output Timing (Example of Port A) ..................................................... 1097

Figure 28.2 Port Data input Timing (Example of Port A) ........................................................ 1098

Section 29 User Break Controller (UBC)

Figure 29.1 Block Diagram of UBC......................................................................................... 1102

Figure 29.2 Flowchart of User Break Debugging Support Function ........................................ 1127

Section 30 User Debugging Interface (H-UDI)

Figure 30.1 H-UDI Block Diagram .......................................................................................... 1136

Figure 30.2 Sequence for Switching from Boundary-Scan TAP Controller to H-UDI ............ 1139

Figure 30.3 TAP Controller State Transitions .......................................................................... 1152

Figure 30.4 H-UDI Reset.......................................................................................................... 1153

Section 31 Electrical Characteristics

Figure 31.1 EXTAL Clock Input Timing ................................................................................. 1161

Figure 31.2 CLKOUT Clock Output Timing (1)...................................................................... 1161

Figure 31.3 CLKOUT Clock Output Timing (2)...................................................................... 1161

Figure 31.4 Power-On Oscillation Settling Time ..................................................................... 1162

Figure 31.5 MODE pins Setup/Hold Timing............................................................................ 1162

Figure 31.6 PLL Synchronization Settling Time ...................................................................... 1163

Figure 31.7 Control Signal Timing........................................................................................... 1163

Figure 31.8 SRAM Bus Cycle: Basic Bus Cycle (No Wait) .................................................... 1165

Figure 31.9 SRAM Bus Cycle: Basic Bus Cycle (One Internal Wait) ..................................... 1166

Figure 31.10 SRAM Bus Cycle: Basic Bus Cycle

Figure 31.11 SRAM Bus Cycle: Basic Bus Cycle (No Wait, No Address Setup/

Figure 31.12 Burst ROM Bus Cycle (No Wait) ....................................................................... 1169

Figure 31.13 Burst ROM Bus Cycle (1st Data: One Internal Wait +

Figure 31.14 Burst ROM Bus Cycle (No Wait, No Address Setup/

Figure 31.15 Burst ROM Bus Cycle (One Internal Wait + One External Wait) ...................... 1172

Figure 31.16 PCMCIA Memory Bus Cycle ............................................................................. 1173

Figure 31.17 PCMCIA I/O Bus Cycle...................................................................................... 1174

Rev.1.00 Dec. 13, 2005 Page xl of l

Hold Time Insertion, RDS = 1, RDH = 0, WTS = 1, WTH = 1)......................... 1168

One External Wait ; 2nd/3rd/4th Data: One Internal Wait)................................. 1170

Hold Time Insertion, RDS = 1, RDH = 0) .......................................................... 1171

(One Internal Wait + One External Wait) ........................................................... 1167

Related parts for R8A77800ANBGAV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: