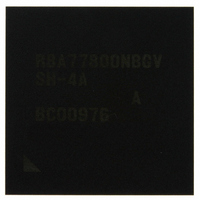

R8A77800ANBGAV Renesas Electronics America, R8A77800ANBGAV Datasheet - Page 23

R8A77800ANBGAV

Manufacturer Part Number

R8A77800ANBGAV

Description

IC SUPERH MPU ROMLESS 449-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77800ANBGV.pdf

(1342 pages)

Specifications of R8A77800ANBGAV

Core Processor

SH-4A

Core Size

32-Bit

Speed

400MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

75

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

1.15 V ~ 1.35 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

449-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77800ANBGAV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 23 of 1342

- Download datasheet (7Mb)

22.4 Operation ........................................................................................................................... 827

Section 23 Serial Protocol Interface (HSPI) ......................................................849

23.1 Features.............................................................................................................................. 849

23.2 Input/Output Pins ............................................................................................................... 851

23.3 Register Descriptions ......................................................................................................... 851

23.4 Operation ........................................................................................................................... 861

22.3.2 Clock Select Register (SISCR) ............................................................................. 804

22.3.3 Control Register (SICTR) ..................................................................................... 806

22.3.4 Transmit Data Register (SITDR) .......................................................................... 809

22.3.5 Receive Data Register (SIRDR) ........................................................................... 810

22.3.6 Transmit Control Data Register (SITCR) ............................................................. 811

22.3.7 Receive Control Data Register (SIRCR) .............................................................. 812

22.3.8 Status Register (SISTR)........................................................................................ 813

22.3.9 Interrupt Enable Register (SIIER)......................................................................... 819

22.3.10 FIFO Control Register (SIFCTR) ......................................................................... 821

22.3.11 Transmit Data Assign Register (SITDAR) ........................................................... 823

22.3.12 Receive Data Assign Register (SIRDAR)............................................................. 824

22.3.13 Control Data Assign Register (SICDAR) ............................................................. 825

22.4.1 Serial Clocks ......................................................................................................... 827

22.4.2 Serial Timing ........................................................................................................ 829

22.4.3 Transfer Data Format............................................................................................ 830

22.4.4 Register Allocation of Transfer Data .................................................................... 832

22.4.5 Control Data Interface .......................................................................................... 834

22.4.6 FIFO...................................................................................................................... 836

22.4.7 Transmit and Receive Procedures......................................................................... 838

22.4.8 Interrupts............................................................................................................... 843

22.4.9 Transmit and Receive Timing............................................................................... 845

23.3.1 Control Register (SPCR)....................................................................................... 852

23.3.2 Status Register (SPSR) ......................................................................................... 854

23.3.3 System Control Register (SPSCR)........................................................................ 857

23.3.4 Transmit Buffer Register (SPTBR)....................................................................... 859

23.3.5 Receive Buffer Register (SPRBR)........................................................................ 860

23.4.1 Operation Overview without DMA (FIFO Mode Disabled)................................. 861

23.4.2 Operation Overview with DMA ........................................................................... 862

23.4.3 Operation with FIFO Mode Enabled .................................................................... 862

23.4.4 Timing Diagrams .................................................................................................. 863

23.4.5 HSPI Software Reset ............................................................................................ 864

23.4.6 Clock Polarity and Transmit Control .................................................................... 864

23.4.7 Transmit and Receive Routines ............................................................................ 864

Rev.1.00 Dec. 13, 2005 Page xxi of l

Related parts for R8A77800ANBGAV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: