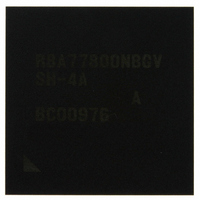

R8A77800ANBGAV Renesas Electronics America, R8A77800ANBGAV Datasheet - Page 16

R8A77800ANBGAV

Manufacturer Part Number

R8A77800ANBGAV

Description

IC SUPERH MPU ROMLESS 449-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77800ANBGV.pdf

(1342 pages)

Specifications of R8A77800ANBGAV

Core Processor

SH-4A

Core Size

32-Bit

Speed

400MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

75

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

1.15 V ~ 1.35 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

449-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77800ANBGAV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 16 of 1342

- Download datasheet (7Mb)

10.5 Operation ........................................................................................................................... 308

10.6 Interrupt Response Time.................................................................................................... 311

10.7 Usage Notes ....................................................................................................................... 312

Section 11 Local Bus State Controller (LBSC)................................................. 315

11.1 Features.............................................................................................................................. 315

11.2 Input/Output Pins............................................................................................................... 318

11.3 Area Overview................................................................................................................... 320

11.4 Register Descriptions......................................................................................................... 329

11.5 Operation ........................................................................................................................... 352

Rev.1.00 Dec. 13, 2005 Page xiv of l

10.4.3 IRL Interrupts ....................................................................................................... 297

10.4.4 On-chip Module Interrupts ................................................................................... 299

10.4.5 Interrupt Priority Levels of On-chip Module Interrupts ....................................... 300

10.4.6 Interrupt Exception Handling and Priority............................................................ 301

10.5.1 Interrupt Sequence ................................................................................................ 308

10.5.2 Multiple Interrupts ................................................................................................ 310

10.5.3 Interrupt Masking by MAI Bit.............................................................................. 310

10.7.1 To Clear Interrupt Request When Holding Function Selected ............................. 312

10.7.2 Notes on Setting IRQ/IRL[7:0] Pin Function ....................................................... 313

10.7.3 To clear IRQ and IRL interrupt requests .............................................................. 313

11.3.1 Space Divisions .................................................................................................... 320

11.3.2 Memory Bus Width .............................................................................................. 324

11.3.3 Data Alignment..................................................................................................... 325

11.3.4 PCMCIA Support ................................................................................................. 325

11.4.1 Memory Address Map Select Register (MMSELR)............................................. 331

11.4.2 Bus Control Register (BCR) ................................................................................. 333

11.4.3 CSn Bus Control Register (CSnBCR) .................................................................. 336

11.4.4 CSn Wait Control Register (CSnWCR)................................................................ 342

11.4.5 CSn PCMCIA Control Register (CSnPCR).......................................................... 347

11.5.1 Endian/Access Size and Data Alignment.............................................................. 352

11.5.2 Areas..................................................................................................................... 357

11.5.3 SRAM interface .................................................................................................... 361

11.5.4 Burst ROM (Clock Asynchronous) Interface ....................................................... 370

11.5.5 PCMCIA Interface................................................................................................ 372

11.5.6 MPX Interface ...................................................................................................... 383

11.5.7 Byte Control SRAM Interface .............................................................................. 389

11.5.8 Wait Cycles between Accesses............................................................................. 393

11.5.9 Bus Arbitration ..................................................................................................... 395

11.5.10 Bus Release and Acquire Sequence...................................................................... 397

11.5.11 Cooperation between Master and Slave................................................................ 399

Related parts for R8A77800ANBGAV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: